Digilent Nexys2: implementacja interfejsu klawiatury PS/2 w VHDL

Ostatnim komponentem jest blok odczytu danych z portu szeregowego PS/2. Blok ten przedstawiono na rysunku 5.

Rys. 5. Komponent odczytu danych z PS/2

Opis sygnałów:

clk_i – wejściowy sygnał zegarowy 75 kHz

rst_i – sygnał reset, który resetuje kaskadę wyświetlaczy

ps2_clk_i – sygnał zegara PS/2 (~15 kHz)

ps2_data_i – sygnał danych PS/2

data_buf_o – szyna danych złożona z 8 bitów, które zostały przesłane przez ps2_data_i

data_ready_io – sygnał, który jest interpretowany jako flaga gotowości odczytu data_buf_o przez układ nadrzędny

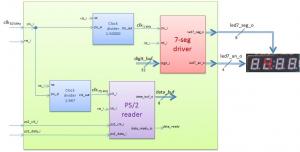

Schemat blokowy projektu przedstawiono na rys. 6.

Rys. 6. Schemat blokowy układu obsługi klawiatury PS/2

Daniel Nitecki

Autoryzowanym dystrybutorem firmy Digilent w Polsce jest Kamami, ul. Lwowska 5, 05-120 Legionowo, http://www.kamami.pl.

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle

Jak model Industry 5.0 wspiera zrównoważony rozwój w polskim przemyśle  Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii