Nowe peryferia w mikrokontrolerach Microchipa, czyli jak ponownie polubić 8-bitowce [3]

W ostatniej części kursu dedykowanego nietypowym peryferiom wbudowanym w mikrokontrolery PIC16 firmy Microchip przedstawimy od strony praktycznej moduł logiki konfigurowalnej CLC.

CLC (Configuration Logic Cell) to kolejny nietypowy moduł mikrokontrolera. Jeżeli się zastanowić, to opisywany w naszym kursie moduł NCO, czy inne zaawansowane peryferia nie są na tyle uniwersalne, by same w sobie mogły być stosowane na szeroką skalę. Samo zaimplementowanie nawet najciekawszych modułów może powodować, że mikrokontroler jednak stanie się układem niszowym. Żeby tak nie było peryferia potrzebują mechanizmu, który pozwoli na logiczne elastyczne łączenie peryferii między sobą. Przykładem takiego połączenia jest budowany przez nas w poprzedniej części cyklu moduł PWM składający się modułu PWM, moduły NCO i układu bramkującego taktowanie. Takim logicznym „klejem” umożliwiającym łączenie wejść i wyjść modułów pomiędzy sobą, ale też wyprowadzanie sygnałów na wyprowadzenia (porty) mikrokontrolera są moduły Configurable Logic Cell – CLC. CLC jest makrocelą z możliwością wyboru jednej z 8 topologii:

- AND-OR

- OR-XOR

- AND

- SR

- D-Flop

- OR-D

- JK

- D Latch

Na wejściu makroceli są 4 czterowejściowe bramki OR z wejściami podłączonymi do selektora sygnałów wejściowych. Wejścia selektora są programowane i można na nie podawać sygnały z wyjść modułów peryferyjnych, wewnętrzne sygnały zegarowe (na przykład HFINTOSC), stany flag przerwań, stany wyjść z innych modułów CLC ale tez sygnały z linii portów.

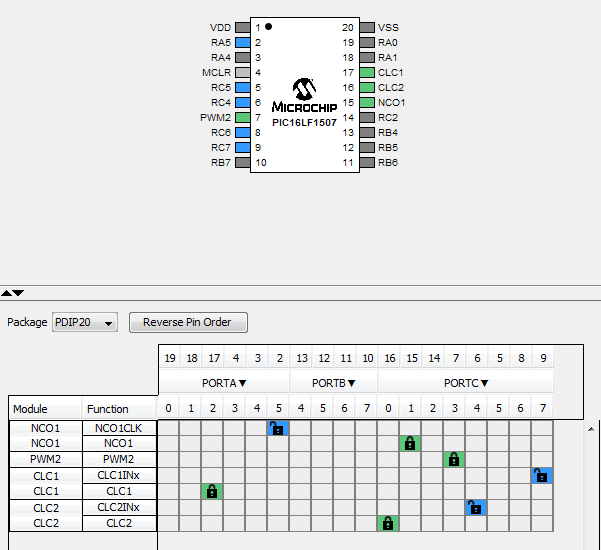

Rys. 24. Przykładowa konfiguracja CLC w topologii AND-OR

Na rysunku 24 pokazano topologię AND-OR z okna MPLAB Code Configurator. Sygnały z 4 wejść są wybierane z rozwijanego menu i kierowane do wejść bramek OR. Przez kliknięcie na krzyżyk przy wejściu bramki OR sygnał jest łączony do wejścia. Ponadto każdy wejście bramki może być zanegowane. Można tez zanegować wyjście każdej z bramki OR (kliknięcie na kwadracik przy wyjściu), oraz zanegować wyjście makroceli. Code Configurator tez umożliwia ręczną konfigurację dostępną po kliknięciu na zakładkę Manual.

Przy korzystaniu z modułów CLC trzeba pamiętać o tym, że

- Operacje logiczne wykonywane w bloku CLC są całkowicie asynchroniczne i niezależne od operacji wykonywanych przez MCU. Również szybkość działania nie jest ograniczana przez częstotliwość taktowania mikrokontrolera (16 lub 32 MHz).

- Konfiguracja każdego z bloków jest kontrolowana przez rejestry SFR umieszczone w pamięci RAM i ta konfiguracja może być dynamicznie zmieniana w trakcie pracy mikrokontrolera. Oczywiście po włączeniu zasilania rejestry sterujące CLC musza być zainicjowane przez mikrokontroler.

- Pobór prądu przez układy logiczne jest w stanie statycznym pomijalnie mały, ale w miarę zwiększania częstotliwości taktowania sygnałów wejściowych narasta liniowo.

Minimalny pobór prądu pozwala wykorzystać CLC w układach bateryjnych, na przykład w układach wybudzania mikrokontrolera ze stanu uśpienia.

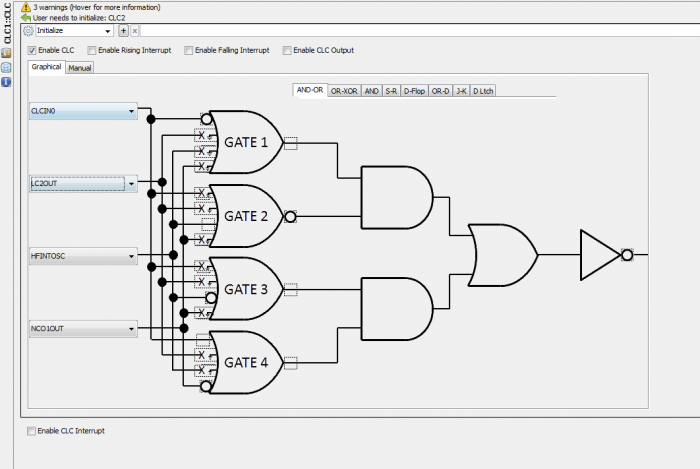

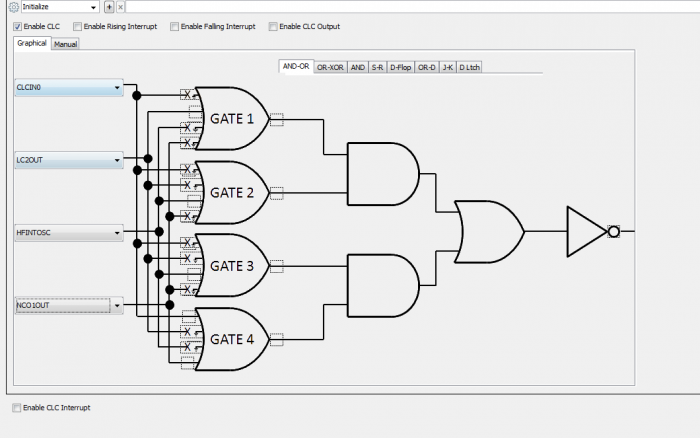

Wróćmy teraz do naszego projektu modułu PWM. Sygnały: zegar taktujący o częstotliwości 16MHz, wejście taktowania i wyjście NCO, oraz sygnał wyjściowy z PWM2 trzeba połączyć według schematu z rysunku 16. Do tego celu wykorzystamy CLC1 w konfiguracji AND-OR. Najpierw sygnał Fosc=16MHz (HFINOSC) łączymy z wejściami bramek GATE2 i GATE3. Do wejścia bramki GATE4 podłączamy wyjście z generatora NCO (NCO1OUT). Pozostaje jeszcze podłączyć do wejścia bramki GATE1 wyjścia z modułu PWM2. Niestety konfiguracja wejść LCC nie pozwala połączyć wyjścia PWM2OUT do żadnego z wejść. Można wybrać PWM3, lub PWM4, ale wtedy trzy sygnały HFINOSC, NCO1OUT i PWM3OUT można wybrać tylko z dwu dolnych wejść. Rozwiązaniem może być wyprowadzenie sygnału PWM2OUT na pin mikrokontrolera, a potem wprowadzenie go za pomocą innego pinu skonfigurowanego jako wejście CLCIN0. Żeby tego nie robić wykorzystałem drugi moduł CLC2 w topologii AND, skonfigurowałem go tak by tylko przenosił sygnał PWM2OUT i jego wyjście LC2OUT wewnętrznie zostało podłączone do wejścia bramki GATE1. Przy takiej konfiguracji nie potrzeba wykonywać żadnych połączeń pomiędzy wyprowadzeniami mikrokontrolera. Na rysunku 25 pokazano konfigurację CLC1 realizująca połączenie sygnałów modułu PWM o dużej rozdzielczości. Sygnał LC2OUT, jest sygnałem PWM2OUT – rysunek 26.

Rys. 25. Połączenie sygnałów modułu PWM o dużej rozdzielczości

Rys. 26. Dołączenie sygnału PWM2OUT do LC2OUT

MPLAB Code Configurator wygenerował na podstawie konfiguracji 2 funkcje inicjalizacji modułów: CLC1 (listing 8) i CLC2 (listing 9).

List. 8. Funkcja inicjalizacji modułu CLC1

void CLC1_Initialize(void) {

// Set the CLC1 to the options selected in the User Interface

// LC1G4POL not_inverted; LC1G1POL not_inverted; LC1G2POL not_inverted; LC1G3POL not_inverted; LC1POL inverted;

CLC1POL = 0x80;

// LC1D1S CLCIN0; LC1D2S LC2OUT;

CLC1SEL0 = 0x50;

// LC1D3S HFINTOSC; LC1D4S NCO1OUT;

CLC1SEL1 = 0x05;

// LC1G1D3T disabled; LC1G1D2T enabled; LC1G1D1T disabled; LC1G1D4N disabled; LC1G1D1N disabled; LC1G1D2N disabled; LC1G1D3N disabled; LC1G1D4T disabled;

CLC1GLS0 = 0x08;

// LC1G2D4N disabled; LC1G2D3N disabled; LC1G2D2N disabled; LC1G2D4T disabled; LC1G2D3T enabled; LC1G2D2T disabled; LC1G2D1N disabled; LC1G2D1T disabled;

CLC1GLS1 = 0x20;

// LC1G3D4N disabled; LC1G3D2N disabled; LC1G3D1N disabled; LC1G3D3N disabled; LC1G3D3T enabled; LC1G3D4T disabled; LC1G3D1T disabled; LC1G3D2T disabled;

CLC1GLS2 = 0x20;

// LC1G4D1T enabled; LC1G4D4T enabled; LC1G4D2N disabled; LC1G4D3N disabled; LC1G4D4N disabled; LC1G4D1N disabled; LC1G4D3T disabled; LC1G4D2T disabled;

CLC1GLS3 = 0x82;

// LC1MODE AND-OR; LC1EN enabled; LCINTP disabled; LCINTN disabled; LC1OUT disabled; LC1OE disabled;

CLC1CON = 0x80;

}

List. 9. Funkcja inicjalizacji modułu CLC2

void CLC2_Initialize(void) {

// Set the CLC2 to the options selected in the User Interface

// LC2G3POL inverted; LC2POL not_inverted; LC2G4POL inverted; LC2G1POL not_inverted; LC2G2POL inverted;

CLC2POL = 0x0E;

// LC2D1S CLCIN0; LC2D2S FOSC;

CLC2SEL0 = 0x00;

// LC2D4S LFINTOSC; LC2D3S PWM2OUT;

CLC2SEL1 = 0x07;

// LC2G1D2N disabled; LC2G1D1N disabled; LC2G1D4N disabled; LC2G1D3N disabled; LC2G1D4T disabled; LC2G1D1T disabled; LC2G1D2T disabled; LC2G1D3T enabled;

CLC2GLS0 = 0x20;

// LC2G2D2N disabled; LC2G2D4T disabled; LC2G2D1N disabled; LC2G2D3T disabled; LC2G2D3N disabled; LC2G2D4N disabled; LC2G2D1T disabled; LC2G2D2T disabled;

CLC2GLS1 = 0x00;

// LC2G3D4N disabled; LC2G3D1T disabled; LC2G3D1N disabled; LC2G3D3N disabled; LC2G3D2N disabled; LC2G3D4T disabled; LC2G3D2T disabled; LC2G3D3T disabled;

CLC2GLS2 = 0x00;

// LC2G4D4T disabled; LC2G4D3T disabled; LC2G4D2T disabled; LC2G4D1T disabled; LC2G4D1N disabled; LC2G4D3N disabled; LC2G4D4N disabled; LC2G4D2N disabled;

CLC2GLS3 = 0x00;

// LC2MODE 4-input AND; LCINTP disabled; LC2OE disabled; LCINTN disabled; LC2OUT disabled; LC2EN enabled;

CLC2CON = 0x82;

}

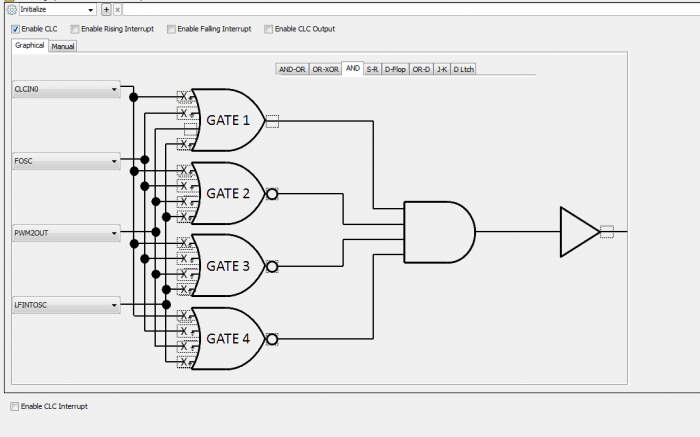

W tym momencie mamy już wszystko by uruchomić nasz moduł PWM o dużej rozdzielczości. Do celów testowych z pomocą PIN Managera wyprowadziłem sygnały: PWM2OUT (LCO2OUT), NCO1CLK (LCO1OUT) i wyjście PWM z naszego modułu (LC1OUT) – rysunek 27.

Rys. 27. Sygnały testowe na wyprowadzeniach mikrokontrolera

Mając do dyspozycji darmowe środowisko MPLAB IDE z bezpłatnym kompilatorem MPLAB XC8 i wtyczką MPLAB Code Configurator byliśmy w stanie zaprojektować i wykonać moduł PWM o dużej rozdzielczości. Żeby wszystko działało nie potrzeba było używać żadnych układów zewnętrznych i wykonywać żadnych połączeń zewnętrznych. Potrzebne układy peryferyjne znalazły się wewnątrz mikrokontrolera PIC18LF1507, a wszystko razem zostało „sklejone” przez konfigurowalną makrocelę LCC. Oczywiście przykład modułu PWM został tak dobrany by pokazać praktyczne możliwości wykorzystania generatora NCO i układów LCC, ale trudno zaprzeczyć, że zbudowanie modułu PWM– bitowym pracującego z częstotliwością 500kHz i rozdzielczością 15bitów jest sporym osiągnięciem

Tomasz Jabłoński

Gaia AI – fabryka sztucznej inteligencji powstaje w Krakowie

Gaia AI – fabryka sztucznej inteligencji powstaje w Krakowie  Alstom realizuje testy nowej technologii AI. Celem jest ochrona dzikich zwierząt w pobliżu linii kolejowych

Alstom realizuje testy nowej technologii AI. Celem jest ochrona dzikich zwierząt w pobliżu linii kolejowych  Battery Forum Poland 2026 – rekordowa edycja targów magazynowania energii już w maju pod Warszawą

Battery Forum Poland 2026 – rekordowa edycja targów magazynowania energii już w maju pod Warszawą