[PRZYKŁADY] Nowe peryferia w mikrokontrolerach Microchipa, czyli jak ponownie polubić 8-bitowce [2]

Uwaga! Wszystkie odcinki artykułu są dostępne pod adresem.

W poprzedniej części kursu przedstawiliśmy programowany generator przebiegów prostokątnych NCO, który można wykorzystać także jako generator precyzyjnego przebiegu PWM. Jak to zrobić przedstawiamy w artykule.

Argument #2 – NCO jako generator przebiegu o dużej rozdzielczości

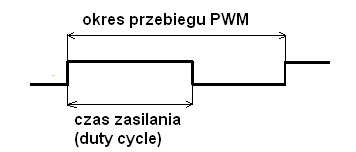

Wiele mikrokontrolerów ma wbudowany standardowy moduł potrafiący generować przebiegi PWM. Przebieg PWM (rysunek 11) jest charakteryzowany przez:

- częstotliwość (okres) cyklu,

- współczynnik wypełnienia, definiowany jako procentowy udział czasu trwania stanu wysokiego do okresu cyklu (duty cycle),

- rozdzielczość, czyli krok z jakim może być zmieniany czas trwania stanu wysokiego.

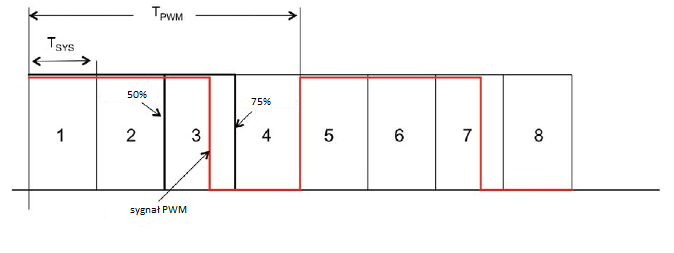

Rys. 11. Typowy przebieg PWM

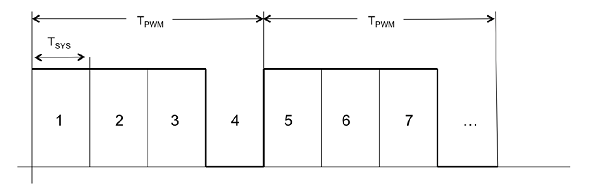

Częstotliwość przebiegu i duty cycle nie wymagają szerszego komentarza. Przyjrzyjmy się teraz problemowi rozdzielczości przebiegu. Rozdzielczość, to „krok” z jakim możemy zmieniać czas zdefiniowany jako duty cycle (rysunek 12).

Rys. 12. Konwencjonalny przebieg PWM

Okres przebiegu PWM oznaczmy Tpwm. W jednym okresie można „zmieścić” N cykli o okresie Tsys – na rysunku 12 będą to 4 cykle (wypełnienie przebiegu 100%). Rozdzielczość bitową przebiegu PWM wylicza się z zależności

![]()

Jak to wygląda w praktyce? Nasz mikrokontroler jest taktowany częstotliwością 16MHz, co daje Tsys =1/16 000 000 = 62,5ns. Jeżeli skonfigurujemy sobie przebieg PWM o Tpwm=200kHz, to czas Tpwm będzie równy 1/200 000 = 5us. W jednym okresie Tpwm zmieści się 80 cykli Tsys, bo 6us/62,5ns=80. Zatem nasze N będzie równe 80, a rozdzielczość bitowa:

![]()

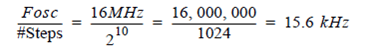

Z tych wyliczeń wynika też inna zależność. Jeżeli PWM jest taktowany określoną częstotliwością i potrzebujemy określonej rozdzielczości bitowej, to ograniczeniu podlega częstotliwość przebiegu PWM. Na przykład jeżeli PWM jest taktowane częstotliwością 16MHz i potrzebujemy rozdzielczości 10-bitowej, to częstotliwość przebiegu PWM nie może być wyższa niż 15,6kHz. Maksymalną częstotliwość przebiegu PWM dla zadanej rozdzielczości bitowej wylicza się z zależności:

Częstotliwość cyklu przebiegu PWM jest wybierana w szerokim zakresie i zależy od rodzaju obciążenia. Jeżeli chcemy sterować jasnością żarówki, to wybieramy wartość z zakresu 100…200Hz. Przełączanie zasilania z tą częstotliwością w połączeniu z bezwładnością rozgrzanego włókna daje efekt ciągłego świecenia z jasnością zależną od czasu załączenia zasilania. Silniki elektryczne są zasilane przebiegami PWM o częstotliwości kilku kHz. Trudno sobie wyobrazić by silnik elektryczny mógł się zatrzymywać i ruszać kilka tysięcy razy na sekundę. Również w tym przypadku charakter obciążenia powoduje, że dostarczana moc jest „uśredniana” mechaniczną bezwładnością silnika

Dioda LED zasilana przebiegiem PWM o częstotliwości kilkuset Hz lub kilku kHz nie będzie uśredniała mocy do niej dostarczonej, ale będzie się cyklicznie zapalała i gasła w takt przebiegu PWM. Efekt postrzegania uśrednionej zmiany jasności świecenia nastąpi w oku, bo nie może ono zarejestrować tak szybkich zmian.

Jak widać w wielu aplikacjach częstotliwość PWM jest dużo wyższa niż układ sterowany może zmieniać swój stan. Sterowana żarówka, lub silnik elektryczny jest swego rodzaju filtrem dolnoprzepustowym uśredniającym sygnał sterujący. W układach elektronicznych stosuje się również klasyczne filtry dolnoprzepustowe. Przykładem może być przetwornik PWM/napięcie, lub szerzej przetwornik cyfrowo analogowy. Jeżeli zastosujemy filtr dolnoprzepustowy filtrujący wyższe harmoniczne przebiegu PWM, to otrzymamy napięcie na wyjściu proporcjonalne do współczynnika wypełnienia przebiegu PWM. Jeżeli rozdzielczość bitowa przebiegu jest mała, to rozdzielczość przetwornika również będzie mała. Zwiększenie precyzji regulacji napięcia można osiągnąć przez zwiększenie rozdzielczości bitowej przebiegu PWM.

Z przedstawionych wyżej rozważań wynika, ze w klasycznym podejściu zwiększenie rozdzielczości można osiągnąć przez zwiększanie częstotliwości taktowania PWM, lub przez zmniejszanie częstotliwości PWM. Oba te sposoby maja ograniczenia. Częstotliwość taktowania nie może być wyższa niż przewidziana dla mikrokontrolera, niskie częstotliwości PWM trudniej się filtruje.

Popatrzmy jeszcze raz na rysunek 12. Czas trwania Tsys Zależy od częstotliwości taktowania PWM i nie może być dowolnie podzielony. Żeby zmniejszyć Tsys dwukrotnie trzeba zwiększyć dwukrotnie taktowanie.

Te ograniczenia mogą być znacznie mniejsze kiedy do generowania przebiegu PWM użyjemy modułu NCO. NCO można użyć do zbudowania wyzwalanego generatora monostabilnego generującego impuls o zadanym czasie trwania. Ponieważ wiemy, że NCO potrafi generować częstotliwości z dużą rozdzielczością, to czas trwania impulsów będzie można również ustawić dużo większą rozdzielczością niż w przypadku klasycznej metody pokazanej na rysunku 12.

Rys. 13. Generowanie sygnału PWM przez układ NCO

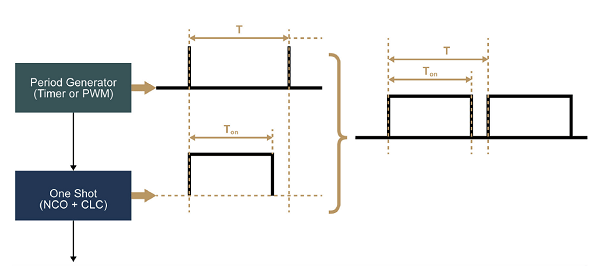

Popatrzmy teraz na rysunek 13. W okresie Tpwm można zmieścić 4 cykle Tsys i przebieg PWM może mieć wypełnienie 25%, 50%, 75% i 100%. Używając generatora monostabilnego zbudowanego z NCO można wygenerować przebieg PWM, którego opadające zbocze może wypadać z określoną dokładnością wewnątrz okresu sygnału Tsys. Kluczem do osiągnięcia wysokiej rozdzielczości sygnału PWM jest wysoka rozdzielczość generowania czasów przez generator NCO. A jak się okazuje w określonych warunkach może być ona dużo wyższa niż w przypadku klasycznej metody stosowanej w standardowych modułach PWM.

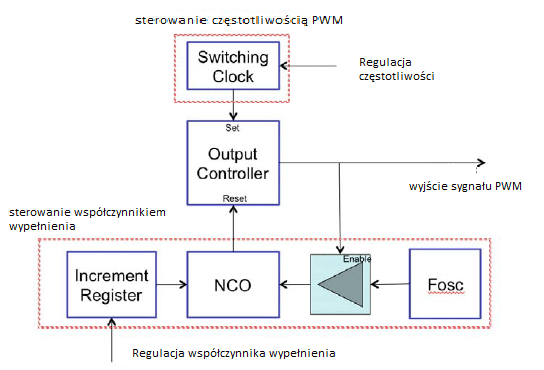

Pozostaje teraz zbudować układ, który będzie wykorzystywał NCO do generowania PWM, bo jak wiadomo z opisu sam NCO nie może generować PWM, a sygnał wyjściowy ma stałe wypełnienie 50%. Jako źródło wyzwalania okresu przebiegu PWM i generatora monostabilnego z układem NCO można użyć na przykład konwencjonalnego sygnału PWM lub jednego z timerów mikrokontrolera. Ogólna idea generatora PWM w wykorzystaniem NCO została pokazana na rysunku 14.

Rys. 14. Idea generatora PWM z wykorzystaniem NCO

Generator okresu (Switching Clock) generuje zbocze co Tpwm. Każde takie zbocze wyzwala generator monostabilny zbudowany z NCO, a czas trwania stanu wysokiego jest określony przez wartość wpisaną do rejestru Increment i wynosi Ton=1/Fnco, gdzie Fnco jest częstotliwością pracy generatora NCO. Zegar taktujący NCO jest bramkowany sygnałem wyjściowym PWM. Przebiegi czasowe w trakcie pracy układu zostały pokazane na rysunku 15.

Rys. 15. Przebiegi czasowe w trakcie pracy generatora PWM

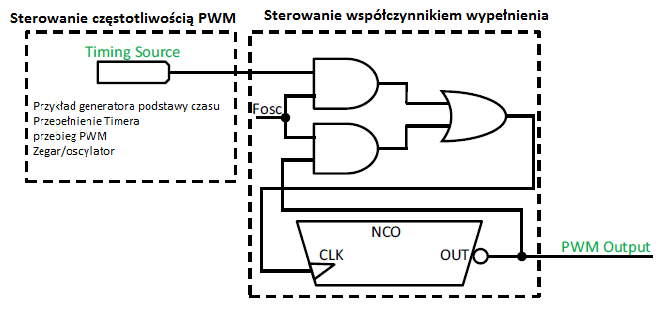

W teorii wygląda to prosto, ale trzeba to jakoś zaimplementować w mikrokontrolerze PIC16LF1507. Oprócz NCO do tego celu potrzebne nam będzie kilka bramek. Tu z pomocą przyjdzie nam kolejny nietypowy moduł: CLC. CLC zostanie opisany dokładniej dalej, ale teraz musimy wiedzieć, że jest to konfigurowalny makro blok Configurable Logic Cell, podobny jak umieszczane w układach FPGA. PIC16LF1507 ma dwa takie bloki i obydwa zostaną użyte w naszym generatorze. Praktyczna realizacja modułu PWM o dużej rozdzielczości została pokazana na rysunku 16.

Rys. 16. Praktyczna realizacja modułu PWM

Konfigurację modułu NCO rozpoczynamy od ustawienia trybu PF. Przypomnijmy: w tym trybie po każdym przepełnieniu się licznika- akumulatora wyjście NCOx przechodzi w stan aktywny pozostaje w tym stanie przez czas równy zaprogramowanej wielokrotności okresu zliczanego sygnału wejściowego (zliczany przez ripple counter). Czas stanu aktywnego (wysoki) i nieaktywnego (niski) zależy od bitu określającego polaryzację NxPOL i wartości wpisanej do bitów NxPWS rejestru konfiguracyjnego NCOxCON.

Działanie układu można przedstawić w kilku krokach:

- Kiedy układ startuje wyjście NCO jest w stanie niskim (popatrzmy ponownie na rysunek 8 w części 1 artykułu), i układ zaczyna odliczać impulsy zegarowe, aż do przepełnienia. Po przepełnieniu NCO generuje na wyjściu impuls o stanie logicznym 1. Dla naszych celów konfigurujemy wyjście NCO tak by jego stan był zanegowany i na wyjściu, kiedy NCO zlicza impulsy jest stan wysoki, po zliczeniu jest generowany impuls o stanie logicznym zero. Wyjście NCO jest jednocześnie wyjściem PWM. Stan wysoki na wyjściu PWM powoduje, że zegara taktujący Fosc jest podawany na wejście CLG modułu NCO i NCO zlicza impulsy.

- Po zliczeniu zaprogramowanej ilości impulsów wyjście NCO przechodzi w stan niski (bo jest zanegowane). Powoduje to zatrzymanie podawania impulsów Fosc na wejście CLK modułu NCO. Wyjście NCO jest w stanie niskim, bo nie może zliczyć zaprogramowanej liczby cykli Fosc impulsów, by dokończyć generowanie impulsu wyjściowego.

- Taki stan trwa do momentu, kiedy na wejściu Timing Source pojawi się stan wysoki (rysunek 15) z układu generowania impulsów z okresem Tpwm.. Na wejście CLK modułu NCO zostanie podanych kilka impulsów Fosc, NCO dokończy zliczanie i wyjście przejdzie w stan wysoki rozpoczynając generowanie następnego okresu przebiegu PWM.

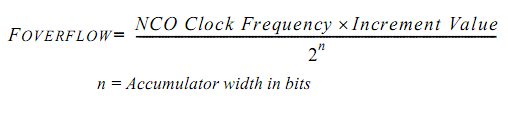

Mamy moduł PWM i oczekujemy teraz wysokiej rozdzielczości sygnału PWM. Wiemy już, że częstotliwość generowana przez moduł NCO jest liniowa i równa:

zatem okres przebiegu wyniesie Tpulse=1/Foverflow. To niestety powoduje, że efektywna rozdzielczość PWM nie jest liniowa(bo funkcja 1/x nie jest liniowa) i zmienia się zależnie od współczynnika wypełnienia.

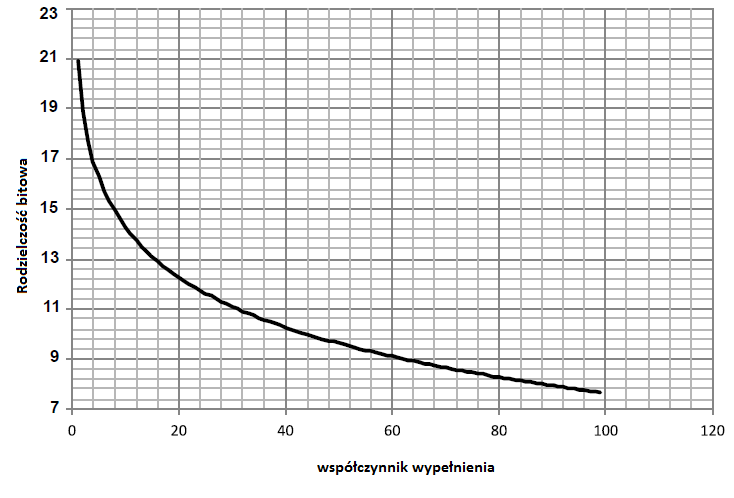

Rys. 17. zależność rozdzielczości bitowej od współczynnika wypełnienia dla Fpwm=3kHz i Fosc=16MHz

Na rysunku 17 pokazano zależność rozdzielczości bitowej dla przebiegu PWM o częstotliwości 3kHz i taktowaniu NCO częstotliwością 16MHz. Dla małego współczynnika wypełnienia osiągamy niesamowitą rozdzielczość 21 bitów, by spaść do rozdzielczości 7,5 bita dla wypełnienia blisko 100%. To dość zaskakujący wynik, bo na końcu zakresu konwencjonalne moduły PWM osiągają lepsze rozdzielczości na przykład 10 bitów).

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników

Daniel Brzeziński z Rochester Electronics opowiada jak skutecznie zarządzać przestrzałością w branży półprzewodników  AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii

AI podważa zasady, które rządziły branżą przez dekady. Moc obliczeniowa staje się nową walutą technologii  Mieszacze aktywne – ćwiczenie z serii ADALM

Mieszacze aktywne – ćwiczenie z serii ADALM