Nanocounter – dokładny miernik częstotliwości wykorzystujący układy FPGA, STM32 oraz aplikację Android

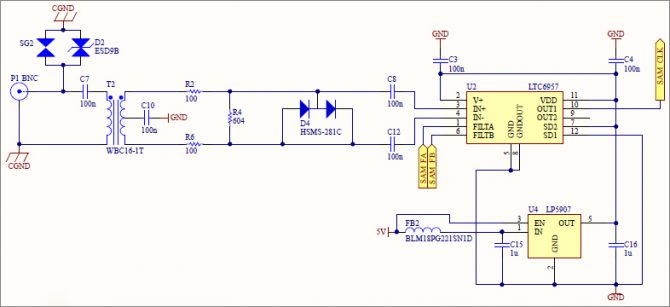

Wejście sygnału mierzonego i referencyjnego

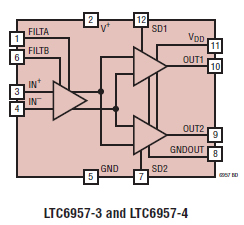

Stopień wejściowy jest oparty na układzie LTC6957. Jest to niskoszumny bufor i układ dystrybucji sygnału, który akceptuje sygnał sinusoidalny lub logiczny o amplitudzie międzyszczytowej poniżej 2 V. Na wyjściu zapewnia sygnał logiczny o stałym poziomie.

Występuje w 4 różnych wersjach z wyjściami logicznymi w standardzie LVPECL, LVDS lub CMOS. Wybrałem model LTC6957IMS-3, który ma wyjście CMOS i kosztuje u Digikey około 5 funtów + podatek.

Firma Linear Technology opublikowała bardzo przydatną notę DN514, która zawiera przykładowy obwód wejściowy dla LTC6957 realizujący dokładnie to, czego potrzebuję.

Iskiernik SG2 oraz dioda chroniąca przed wyładowaniami elektrostatycznymi D2 zapewniają ochronę przed skokami napięcia wejściowego, które mogą wystąpić, gdy użytkownik poruszy złącze BNC. Kondensator C7 odsprzęga składową stałą sygnału, zanim ten trafi na transformator T2. Z kolei diody Schottky’ego stanowią ogranicznik napięcia na wejściach LTC6957.

To tylko krótki opis działania układu. Zachęcam do przeczytania noty DN514, która zawiera szczegółowy opis autorstwa inżynierów Linear Tech.

Układ LTC6957 umożliwia wybór jednego z trzech wąskopasmowych filtrów na częstotliwość 500, 160 lub 50 MHz. Najlepsza opcja będzie zależeć od sygnału wejściowego, zatem zdecydowałem się na podłączenie wyprowadzeń filtru do wejść GPIO mikrokontrolera – dzięki temu mogę wybrać rodzaj filtru za pomocą interfejsu użytkownika.

Układ LTC4957 jest zasilany z niskoszumnego regulatora napięcia LP5907 typu LDO firmy Texas Instruments.

Przedstawiony stopień wejściowy odpowiada za sygnał mierzony. Wejście sygnału referencyjnego jest praktycznie takie samo. Jedyną różnicą jest fakt, że podłączyłem wyjście wyłączające LTC6957 do pinu GPIO mikrokontrolera, dzięki czemu mogę wyłączyć sygnał wejściowy, gdy używane jest wbudowane źródło referencyjne.

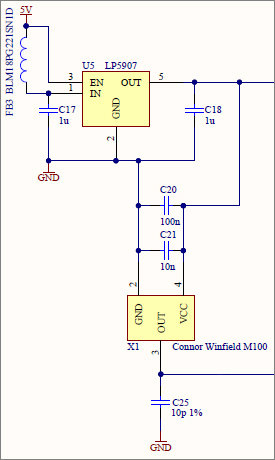

Wbudowany oscylator referencyjny

Stabilność i tolerancja zegara referencyjnego jest kluczowa dla dokładnych pomiarów częstotliwości. Potrzebuję czegoś bardziej dokładnego od oscylatorów kryształowych, które zamierzam mierzyć – w praktyce może to być oscylator z kompensacją temperaturową (TCXO) lub oscylator stabilizowany termicznie (OCXO).

Cena tych układów zależy bezpośrednio od ich stabilności – bardzo szybko stają się drogie. Ponieważ postanowiłem dodać możliwość podłączenia zewnętrznego źródła referencyjnego w przypadku, gdy wymagana jest ponadprzeciętna dokładność, zdecydowałem się na stosunkowo wysokiej klasy oscylator TCXO Connor Winfield M100F. Jest stabilność to 100 ppb (części na miliard), a cena na Digikey to 14 funtów plus podatek.

Istnieją bardziej stabilne układy TCXO i jeszcze bardziej stabilne OCXO, ale przekraczają wymagania mojego projektu. Na ebayu dostępne są też tanie, używane układy OCXO i VCOCXO, ale jestem do nich bardzo sceptycznie nastawiony – zostały wystawione na sprzedaż z powodu swojego wieku i najpewniej utraciły pierwotną specyfikację. W przypadku oscylatorów VCOCXO oznacza, że wyszły poza zakres, w którym korekcja napięcia jest skuteczna.

Ten oscylator TCXO kompensuje częstotliwość wyjściową w oparciu o zaprogramowaną fabrycznie krzywą temperatury. Nadal będzie on dryfował z temperaturą, ale znacznie wolniej, niż standardowy oscylator kryształowy (będzie to dobrze widoczne na filmikach towarzyszących artykułowi). Lepsza odporność na zmiany temperatury otoczenia można uzyskać, stosując OCXO, ale u popularnych dystrybutorów są one naprawdę drogie.

Karta katalogowa M100 podaje pojemność wyjściową obciążenia równą 15 pF. Wahania tej wartości mogłyby zmienić częstotliwość wyjściową o 20 ppb na każdy pikofarad. Natomiast karta katalogowa FPGA podaje zakres pojemności wejściowej od 3 do 10 pF, a wartość typowa nie jest określona. Mając nadzieję, że będzie to około 5 pF, dodałem kondensator C25 na wyjściu oscylatora, aby zwiększyć obciążenie. Nie ma znaczenia, czy wartość będzie odbiegała od idealnej, ponieważ ten błąd jest stały i można go skompensować poprzez kalibrację.

Pętla fazowa (PLL)

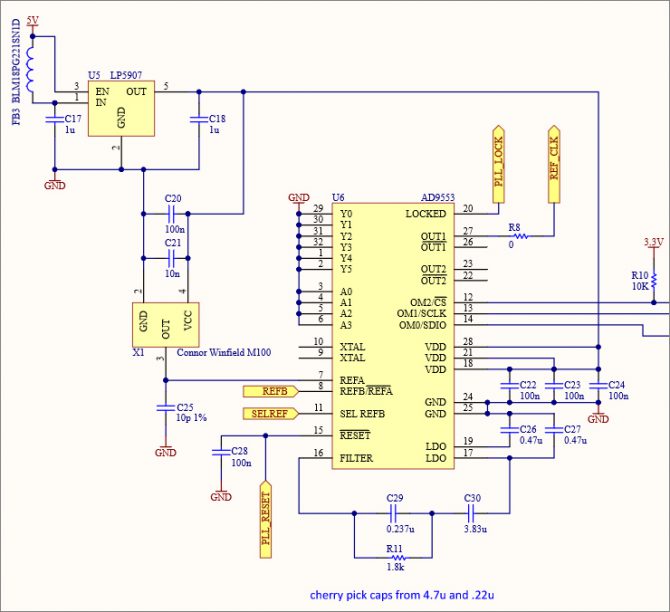

Celem PLL jest zwiększenie częstotliwości referencyjnej do 200 MHz, dzięki której układ FPGA będzie w stanie pracować jako licznik z dużą szybkością. Każdy, kto spotkał się z układami FPGA Xilinx może się w tym momencie zastanowić, dlaczego nie użyłem wbudowanego układu zarządzania zegarem (DCM) w modelu Spartan 3. Niestety ten pomysł odpada, ponieważ minimalna częstotliwość zegara na wejściu DCM jest równa 18 MHz, co więcej jitter średniokwadratowy wynosi 250 ps – to dużo w porównaniu z 1 ps w przypadku innych proponowanych układów. Wybrałem zewnętrzny układ PLL AD9553 od Analog Devices. To model wysokiej klasy z niskim poziomem jitteru, choć umieszczony w niepraktycznej obudowie QFN.

Układ AD9553 ma wiele funkcji i musi być zaprogramowany z zewnątrz za pomocą interfejsu SPI, zanim pętla będzie w stanie się zsynchronizować i generować docelową częstotliwość.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485