Rodzina mikrokontrolerów NXP LPC54000 – przegląd cech i możliwości 2-rdzeniowców Cortex-M

Mikrokontrolery serii LPC54000 produkowane przez firmę NXP są oparte na bardzo popularnej serii mikrokontrolerów LPC1700. Nowa seria została tak zaprojektowana, by sprostać nowym wymaganiom stawianym przez rynek, zachowując przy tym maksymalną kompatybilność „w dół”. W tym celu wprowadzono szereg istotnych innowacji. Najważniejsza z nich to zastosowanie rdzenia Cortex-M4 oraz możliwość zastosowania architektury dwurdzeniowej. Drugim rdzeniem (koprocesorem) może być – w wybranych modelach mikrokontrolerów – jednostka Cortex-M0+.

Obecnie seria LPC54000 jest podzielona na trzy podrodziny:

- LPC5410x MCU Family,

- LPC5411x MCU Family,

- LPC546xx MCU Family.

Rodzina LPC5410x MCU

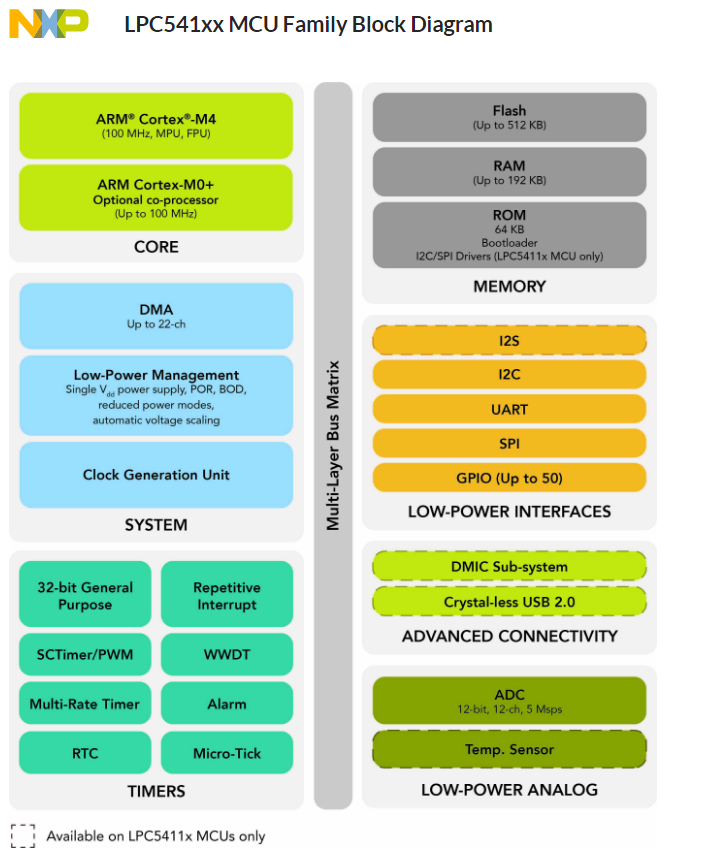

W dniu pisania artykułu rodzina LPC5410x składa się z 8 typów mikrokontrolerów, których najważniejsze cechy zestawiono w tabeli 1. Na rysunku 1 pokazano schemat blokowy rodzin LPC5410x i LPC5411x.

Tab. 1. Mikrokontrolery rodziny LPC5410x

Jak widać w przedstawionym zestawieniu są tu zarówno jednostki z jednym rdzeniem Cortex-M4, a jak i dwurdzeniowe z koprocesorem Cortex-M0+. Wersje 2-rdzeniowe mogą być wykorzystywane w aplikacjach wrażliwych na pobór energii – na przykład w urządzeniach zasilanych bateryjnie. Kiedy nie jest potrzebna wysoka wydajność można użyć rdzenia Cortex M0+, optymalizowanego konstrukcyjnie dla niskiego poboru mocy. Wydajny rdzeń Cotrex-M4 jest włączany w momencie wykonywania algorytmów wymagających dużej mocy obliczeniowej.

Do zarządzaniem poborem energii zastosowano rozwiązanie nazwane Low-Power Management. Ma ono za zadanie zarządzać trybami oszczędzania energii , w tym również przez skalowanie wielkości napięcia zasilania zależnie od wymaganej wydajności. Głównym elementem systemu oszczędzania energii jest programowany układ PMU – Power Management Unit. Pozwala on na wprowadzanie trybów oszczędzania energii: sleep, deep-sleep i deep power-down. Jest możliwość wybudzania z trybu deep-sleep po odebraniu danych przez interfejsy USART, SPI lub przez I2C pracujący w trybie slave.

Rdzenie mogą być taktowane częstotliwością do 100 MHz (oba wykorzystują ten sam zegar taktujący). Układ generowania zegara taktującego rdzeń może pochodzić z dwóch źródeł:

- z wbudowanego wewnętrznego zegara FRO (Free Running Oscillator) zawierający oscylator RC o częstotliwości 12 MHz. Moduł FRO ma dwa wyjścia. Na jednym z nich generuje częstotliwości 48 MHz lub 96 MHz, a na drugim częstotliwość 12 MHz. Częstotliwość oscylatora RC jest generowana z dokładnością 1% w całym zakresie napięć zasilających i dopuszczalnych temperatur pracy.

- zewnętrznego oscylatora kwarcowego o częstotliwości do 25 MHz.

Dokładną żądaną częstotliwość taktowania rdzenia można zaprogramować używając do tego celu układu PLL. Sygnałem wejściowym dla PLL może być zarówno częstotliwość 12 MHZ z modułu FRO, jak i częstotliwość z oscylatora kwarcowego.

Oprócz zegara taktującego rdzeń wbudowano też niezależny oscylator dla watchdoga i oscylator o częstotliwości 32,768 kHz do taktowania modułu zegara systemowego RTC.

Duża wydajność i uniwersalność mikrokontrolerów LPC5410x powoduje, że będą używane do pracy w aplikacjach wymagających rozbudowanego oprogramowania. Jak możemy zobaczyć w zestawieniu pokazanym w tablicy 1 dostępna jest w nich (zależnie od modelu) pamięć programu Flash o pojemności do 512 kB i pamięć danych SRAM o pojemności do 102 kB. Te pojemności pozwalają na umieszczenie w pamięci rozbudowanych procedur, ale też na przykład bitmap i tablic generatorów znaków używanych w interfejsach graficznych.

Oprócz programowanej pamięci programu Flash umieszczono w strukturze mikrokontrolerów pamięć ROM z „zaszytymi” modułami programowania pamięci Flash przez interfejs ISP (In System Programming), IAP (In Application Programming) oraz bootloaderem pozwalającym na programowanie pamięci Flash przez interfejsy szeregowe USART, SPI, I2C oraz USB. W pamięci ROM są też umieszczone drivery USB: HID, CDC, MSC oraz DFU.

Rdzeń ARM Cortex-M4 pracujący samodzielnie lub z koprocesorem ARM Cortex-M0+ oraz duża pamięć programu Flash i SRAM gwarantują dużą wydajność mikrokontrolerów. Zobaczmy teraz jak wygląda kolejny bardzo ważny czynnik mocno decydujący o przydatności w układach wbudowanych i układach IoT, czyli wyposażenie w układy peryferyjne.

Interfejsy szeregowe

Interfejsy szeregowe są umieszczone w module Flexcomm. Zawiera on 8 urządzeń peryferyjnych, z których każdy może być indywidualnie zaprogramowany jako: USART, SPI, I2C, lub I2S (tylko w dwóch urządzeniach peryferyjnych). Interfejsy UART, SPI i I2S są wyposażone w bufor FIFO. Interfejsy I2C można zaprogramować do pracy z prędkością do 1 Mb/s, a dwa z nich z prędkością do 3,4 Mb/s, ale tylko w trybie slave. Taktowanie każdego z dostępnych interfejsów zapewnia rozbudowany generator taktujący Baud Rate Generator. Moduł Flexcomm jest bardzo wygodny, bo nie zakłada na sztywno ile i jakich interfejsów jest umieszczonych w obudowie mikrokontrolera.

Timery

Pięć standardowych 32-bitowych liczników może współpracować maksymalnie czterema wejściami przechwytującymi (capture) i czterema wyjściami typu compare. Każdy z tych liczników można zaprogramować do pracy w trybie PWM i cztery z nich może zliczać impulsy z zewnętrznego wejścia (wyprowadzenia mikrokontrolera). Do generowania żądania transferu w kanale DMA można wybrać zdarzenie generowane przez jeden z timerów. Timer SCTimer/PWM ma osiem wejść i osiem wyjść. Wyjścia i wejścia mogą być programowo przyłączane do i z zewnętrznych wyprowadzeń mikrokontrolera, ale też do wewnętrznych sygnałów innych układów peryferyjnych.

Wbudowany w mikrokontroler 32-bitowy zegar czasu rzeczywistego RTC odlicza czas z rozdzielczością 1 sekundy i nigdy nie jest usypiany. Może być wykorzystywany do wybudzania mikrokontrolera z trybów niskiego poboru energii w tym z trybu deep power-down z rozdzielczością 1 milisekundy.

Interfejsy cyfrowe

W skład interfejsów cyfrowych wchodzi: kontroler DMA oraz układy linii wejścia-wyjścia GPIO. Kontroler DMA ma 20 kanałów i 20 wejść wyzwalających. Umożliwia transfer danych z wszystkich układów peryferyjnych wpierających DMA

Uniwersalne linie GPIO mogą mieć programowo dołączane rezystory pull_up (do plusa zasilania) lub pull-down (do masy). Można je zaprogramować z wyjściem typu otwarty dren (open drain) lub z zanegowanym wejściem (input inverter). Żeby manipulacje stanami linii GPIO mogły się odbywać z dużą prędkością rejestry GPIO zostały połączone do magistrali AHB mikrokontrolera. Zmiany stanów na liniach GPIO mogą po odpowiedniej konfiguracji generować przerwania zewnętrzne. Dostępne jest programowe wybranie wyzwalania zboczem narastającym, zboczem opadającym, lub oboma zboczami. Można tez zgrupować dwie linie wejściowe i zdefiniować warunek wyzwalania przerwania połączony z funkcjami logicznymi AND lub OR.

Interfejsy analogowe

Głównym interfejsem analogowym jest przetwornik analogowo cyfrowy ADC z 12 kanałami pomiarowymi i wieloma wewnętrznymi i zewnętrznymi sygnałami wyzwalającymi pomiar i konwersję. Maksymalna prędkość próbkowania wynosi 5 MS/s. Przetwornik wspiera dwie niezależne sekwencje konwersji analogowo-cyfrowej.

Drugim interfejsem analogowym jest wbudowany czujnik temperatury współpracujący z przetwornikiem ADC.

Moduły ewaluacyjne

Każdy producent mikrokontrolerów oferuje dla swoich wyrobów moduły ewaluacyjne. Jest to standardowe postępowanie ułatwiające znacznie konstruktorom szybkie zapoznanie się z wybranym elementem i ewentualna weryfikacja możliwości układu, środowiska projektowego, wsparcia programistycznego w postaci gotowych bibliotek itp. Dla rodziny LPC541xx MCU producent przygotował moduł OM1307.

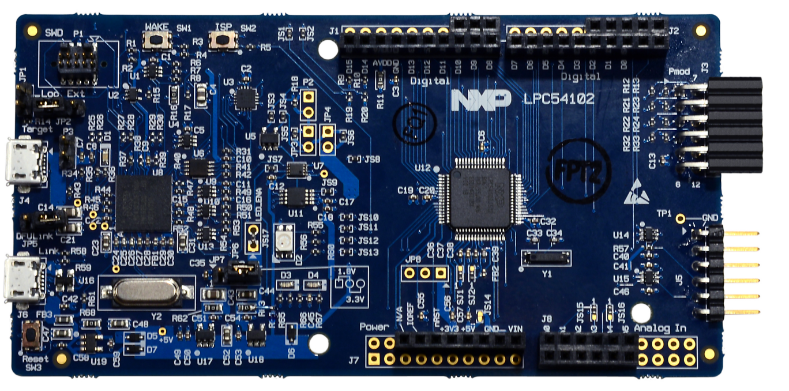

Moduł OM13077 LPCXpresso54102

Moduł ewaluacyjny OM13077 pokazany na fotografii 2 jest elementem składowym platformy LPCXpresso. LPCXpresso składa się z uproszczonego środowiska programistycznego IDE opartego na Eclipse i przeznaczonego dla mikrokontrolerów firmy NXP z rdzeniem ARM oraz tanich dedykowanych modułów ewaluacyjnych z wbudowanym programatorem/debuggerem. Jest to kompletne rozwiązanie umożliwiające inżynierom szybkie przetestowanie możliwości zastosowania mikrokontrolera w swoich aplikacjach. LPCXpresso54102 ma zabudowany mikrokontroler LPC54102. I jest podzielony funkcjonalnie na dwie części: programatora/debuggera i mikrokontrolera.

Programator/debugger jest połączony z komputerem, na którym jest uruchomione IDE poprzez złącze USB. Obsługiwane są protokoły CMSIS-DAP i Redlink. Można go również wykorzystać do programowania mikrokontrolerów użytych w innych urządzeniach.

Zestaw wyposażono m.in. w trójkolorową diodę LED, przyciski RESET, ISP i WAKE. Płytka ma wyprowadzenia linii portów i zasilania zgodne ze standardem Arduino UNO. Znajdziemy tam też port PMOD oraz port UART/FTDI (emulacja UART poprzez USB) . Układ zasilania zawiera stabilizatory 1,8 V oraz 3,3 V. Możliwe jest zasilania z portu USB lub z zewnętrznego zasilacza.

Zero8: nowoczesne złącza firmy EPT w automatyce przemysłowej

Zero8: nowoczesne złącza firmy EPT w automatyce przemysłowej  Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań

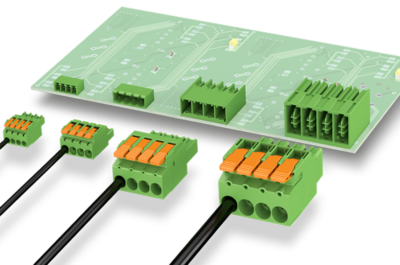

Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań  Nowe generacje złączy: innowacyjne metody połączeń w elektronice

Nowe generacje złączy: innowacyjne metody połączeń w elektronice