Obsługa I2C w trybie Fast-mode Plus w LPC1300

Przykład wykorzystania magistrali I2C w trybie Fast-mode Plus:

while(1)

{

/* Zapisz do PCA9674 0xFF, by skonfigurować wejścia/wyjścia i odczytaj ponownie stan wejść */

/* Zapisz SLA(W), dane(0xFF), SLA(R) i odczytaj ponownie 2 bajty. */

I2CWriteLength = 2;

I2CReadLength = 2;

I2CMasterBuffer[0] = PCA9674_ADDR;

I2CMasterBuffer[1] = 0xFF;

I2CMasterBuffer[2] = PCA9674_ADDR | RD_BIT;

I2CEngine();

/* PCA9674 P0 jako przełącznik FM+(1Mbps) i standardowym/FM(400Kbps) I2C */

if (I2CSlaveBuffer[0] & 0x01)

{

/* I2C FM+ mode */

LPC_IOCON->PIO0_4 &= ~0x0000031F; /* konfiguracja wejścia/wyjścia I2C FM+*/

LPC_IOCON->PIO0_4 |= 0x00000101; /* I2C FM+ SCL */

LPC_IOCON->PIO0_5 &= ~0x0000031F;

LPC_IOCON->PIO0_5 |= 0x00000101; /* I2C FM+ SDA */

/*--- Ustaw prędkość transmisji 1Mbps ---*/

LPC_I2C->SCLL = 48;//24;//0x18;

LPC_I2C->SCLH = 48;//24;//0x18;

}

else

{

/* I2C standard/FM */

LPC_IOCON->PIO0_4 &= ~0x1F; /* konfiguracja wejścia/ wyjścia I2C */

LPC_IOCON->PIO0_4 |= 0x01; /* I2C SCL */

LPC_IOCON->PIO0_5 &= ~0x1F;

LPC_IOCON->PIO0_5 |= 0x01; /* I2C SDA */

/*--- Przywróć prędkość transmisji 62.5Kbps ---*/

LPC_I2C->SCLL = 96;//192;//384;//2400;//0x180;

LPC_I2C->SCLH = 96;//192;//384;//2400;//0x180;

}

/* Zapisz SLA(W), data1 */

I2CWriteLength = 2;

I2CReadLength = 0;

I2CMasterBuffer[0] = PCA9674_ADDR;

I2CMasterBuffer[1] = (I2CSlaveBuffer[0] << 4) | 0x0F;

I2CEngine();

/* Zapisz do PCA9632 parametry konfiguracyjne do migania diodami */

/* Zapisz SLA(W), CON, 00H ~ 0Ch */

I2CWriteLength = 6;

I2CReadLength = 0;

I2CMasterBuffer[0] = PCA9632_ADDR;

I2CMasterBuffer[1] = 0xC2; // Rejestr kontrolny

I2CMasterBuffer[2] = temp; // PWM0

I2CMasterBuffer[3] = temp + 0x40; // PWM1

I2CMasterBuffer[4] = temp + 0x80; // PWM2

I2CMasterBuffer[5] = temp + 0xC0; // PWM3

I2CEngine();

/* Zaktualizuj jasność */

temp1++;

temp = temp + (((temp1 % 2) == 0) ? 1 : 0);

}

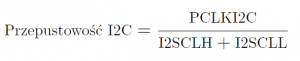

Aby wybrać prędkość transmisji I2C należy zmodyfikować wartości rejestrów I2SCLH i I2SCLL. I2SCLH określa liczbę cykli zegara PCLK_I2C w stanie wysokim linii SCL, natomiast I2SCLL określa liczbę cykli zegara PCLK_I2C w stanie niskim. Częstotliwość pracy magistrali I2C jest zdefiniowana wzorem przedstawionym na rysunku 2, gdzie PCLK_I2C jest taktowaniem zegara systemowego.

Rys. 2. Wzór na częstotliwość pracy magistrali I2C

Tabela 4. Konfiguracje szybkości I2C

| Stan | Przepustowość I2C | Tryb I2C | PCLKI2C | I2SCLH | I2SCLL |

| 1 2 3 4 5 6 |

10 Kbps 62.5 Kbps 125 Kbps 250 Kbps 500 Kbps 1000 Kbps |

Tryb standardowy/Fast-mode I2C Tryb standardowy/Fast-mode I2C Tryb standardowy/Fast-mode I2C Tryb standardowy/Fast-mode I2C Fast-mode Plus I2C Fast-mode Plus I2C |

48 MHz 48 MHz 48 MHz 48 MHz 48 MHz 48 MHz |

2400 384 192 96 48 24 |

2400 384 192 96 48 24 |

Wnioski

W dzisiejszych czasach od pojedynczego kanału I2C wymagana jest jednoczesna obsługa wielu różnych funkcji, jak na przykład uwierzytelnianie produktu, odczyty EEPROM, pomiar temperatury i zarządzanie systemem zasilania. Z tego powodu, wydajność stała się kluczowym problemem. Zintegrowany w LPC1300 kontroler Fast-mode Plus dostarcza prostego sposobu na poprawienie wydajności magistrali I2C ponad dwa razy bez dodatkowych kosztów lub zwiększonej komplikacji układu. Jedynym istotnym wymaganiem poprawnego działania magistrali I2C jest zapewnienie parametrów elektrycznych takich jak pojemność i dołączenie odpowiednich terminatorów. W ofercie NXP znajduje się wiele urządzeń zdolnych do pracy z magistralą I2C w trybie FM.

Artykuł opracowano na podstawie noty aplikacyjnej AN10900 firmy NXP.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485