Projektowanie systemów cyfrowych z wykorzystaniem izolatorów

Rezystancja strat Rl reprezentuje straty powstające wskutek prądu upływu na niskich częstotliwościach. Rd i Cd symbolizują straty wskutek polaryzacji cząstek (Rd) i absorpcji molekuł (Cd). Rs przedstawia rezystancję doprowadzeń i okładek kondensatora. Trzy rezystancje strat zostały połączone w zastępczą rezystancję szeregową. Podobnie jak w przypadku rezystancji zastępczej, indukcyjność zastępcza stanowi połączenie indukcyjności okładek kondensatora i doprowadzeń wewnętrznych.

Warto zauważyć, że kondensator łączący przelotki, choć posiada niską impedancję, wnosi istotny wkład do indukcyjności szeregowej. Z tego powodu należy zmniejszyć indukcyjność przelotek poprzez stosowanie dwóch przelotek na zacisk kondensatora.

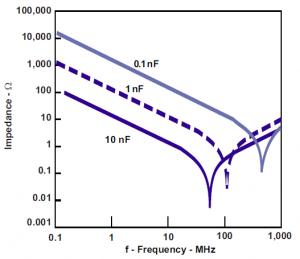

Rysunek 24 pokazuje przebieg impedancji kondensatora w funkcji częstotliwości dla kondensatora 10 nF. Dla częstotliwości znacznie poniżej częstotliwości rezonansowej, dominująca jest reaktancja pojemnościowa. Wraz ze zbliżaniem się do stanu rezonansu, reaktancja indukcyjna zaczyna mieć znaczenie i neutralizuje część pojemnościową. Na częstotliwości rezonansowej reaktancje pochodzące od pojemności i indukcyjności się znoszą i wpływ ma tylko rezystancja zastępcza. Należy zauważyć, że rezystancja szeregowa jest zależna od częstotliwości i, wbrew popularnemu stwierdzeniu, nie osiąga minimum w rezonansie. Impedancja Z, owszem.

Rys. 24. Impedancja kondensatora w funkcji częstotliwości

Powodem, dla którego równoległe łączenie kondensatorów w rozproszonej sieci odsprzęgającej okazuje się skuteczne, jest fakt, iż całkowita pojemność Ctot rośnie do wartości C x n, gdzie n jest liczbą użytych kondensatorów odsprzęgających. Ponieważ Xc = 1/(ω x C), impendancja kondensatora jest zredukowana do wartości Xc = 1/(n x ω x C) dla częstotliwości poniżej rezonansu. Podobnie dzieje się dla indukcyjności. W tym wypadku Ltot = L/n, a ponieważ Xl = ω x L, impedancja maleje do Xl = ω x L/n dla częstotliwości powyżej stanu rezonansu.

Podsumowanie

Celem niniejszego opracowania było przedstawienie głównych aspektów projektowania płytek PCB z izolatorami cyfrowymi. Mając na uwadze ogromne ilości literatury technicznej, seminariów, ogłoszeń i forów dyskusyjnych poświęconych projektowaniu PCB, w tej nocie zawarto wskazówki dotyczące projektowania topografii, które ujęte zostały w zwarty sposób. Kierując się wskazówkami przedstawionymi powyżej, projektanci mogą otrzymać projekty płytek o zadowalającej EMC w możliwie krótkim czasie.

Opracowanie wykonane na podstawie noty aplikacyjnej Texas Instruments SLLA284: Digital Isolator Design Guide; styczeń 2009.

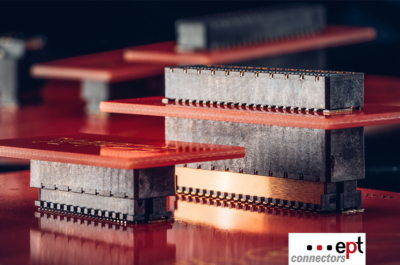

Zero8: nowoczesne złącza firmy EPT w automatyce przemysłowej

Zero8: nowoczesne złącza firmy EPT w automatyce przemysłowej  Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań

Dwukierunkowy przełącznik GaN klasy 650 V do falowników energii słonecznej, centrów danych AI i innych zastosowań  Nowe generacje złączy: innowacyjne metody połączeń w elektronice

Nowe generacje złączy: innowacyjne metody połączeń w elektronice