Interfejs DCMI w STM32: jak dołączyć kamerę CCD do mikrokontrolerów STM32F2 i STM32F4

Krótka charakterystyka kamery MT9D111

W projekcie wykorzystano moduł z 2-megapikselową kamerą posiadającą czujnik obrazu kolorowego MT9D111 z matrycą typu CMOS (fotografia 5). System jaki jest zintegrowany w tym czujniku (SOC, system-on-a-chip) umożliwia łatwe konfigurowanie bogatej listy parametrów oraz oferuje wiele funkcji, jakie są dostępne w fotograficznych aparatach cyfrowych, takie jak ożywianie, korekcja kolorów, korekcja gammy, automatyczny balans bieli, automatyczna ekspozycja oraz wiele innych pozwalających uzyskać zdjęcia możliwie wysokiej jakości.

Fot. 3. Moduł z kamerą MT9D111

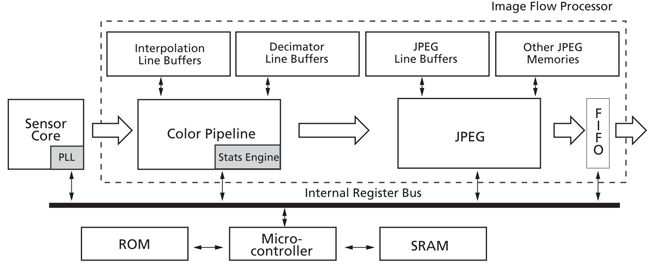

Strukturę blokową systemu SOC przedstawiono na rysunku 4, można w niej wyróżnić cztery najważniejsze elementy: jądro czujnika (Sensor Core), zaawansowany procesor obrazów przepływu (IFP, Image Flow Processor), koder JPEG czasu rzeczywistego oraz mikrokontroler (MCU). Zarejestrowany obraz z matrycy CMOS należącej do jądra czujnika przepływa (gruba biała strzałka) przez poszczególne bloki systemu SOC, w których jest poddawany kolejnym etapom obróbki, a jedną z cech charakterystycznych systemu jest możliwość wybrania bloku z którego dane obrazu będą wysyłane na wyjście modułu. Natomiast sterowanie pracą poszczególnych elementów systemu odbywa się za pomocą wewnętrznej szyny (Internal Register Bus).

Rys. 4. Schemat blokowy systemu SOC

Wybrany moduł z kamerą jest wyposażony w szeregowy interfejs sterujący oraz równoległy interfejs danych wideo z sygnałami synchronizującymi. Na rysunku 5 pokazano rozmieszczenie sygnałów na płytce modułu, a tabela 2 zawiera szczegółowy ich opis. Do zasilania kamery zaleca się podanie 3 V, gdyż napięcia wyższe (nawet 3,3 V), jeśli nawet nie są tragiczne w skutkach, to mogą powodować grzanie się elementów kamery.

Rys. 5. Wyprowadzenia modułu z kamerą (widok od strony obiektywu kamery)

Tab. 2. Opis wyprowadzeń modułu kamery

| Nazwa wyprowadzenia | Rodzaj wyprowadzenia | Opis |

| VCC | Power | Napięcie zasilania kamery, max. 3,1 V |

| GND | Ground | Masa |

| SCL | Input | Linia zegarowa magistrali I2C |

| SDA | Input/Output | Linia danych magistrali I2C |

| VSYNC | Output | Sygnał synchronizujący (FrameValid); stan wysoki – aktywny |

| HREF | Output | Sygnał synch. (LineValid, DataValid, HSYNC); stan wysoki – aktywny |

| PCLK | Output | Wyjściowy sygnał zegarowy taktujący kolejne piksele obrazu |

| XCLK | Input | Wejściowy sygnał zegarowy |

| D7-D0 | Output | 8-bitowa szyna danych wyjściowych |

| STANDBY | Input | Linia sterująca trybem standby |

| DRIVER_IN | Output | Sygnał PWM pochodzący z czujnika kamery |

| DRIVER_EN | Input | VCM (Voice Coil Motor) driving Voltage from Driver |

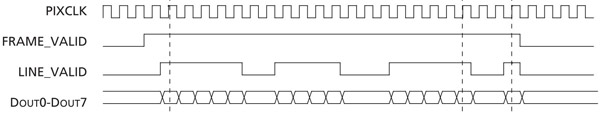

Sposób w jaki ramki wideo są wysyłane przez synchroniczny interfejs równoległy jest łatwy w zrozumieniu. Każdy obraz generowany przez kamerę posiada określoną szerokość oraz wysokość i niech będzie to wymiar 320 x 240 pikseli (matryca pikseli o wymiarach 320 kolumn na 240 wierszy). Do opisu pojedynczego piksela obrazu potrzebnych jest zazwyczaj dwa bajty (np. w formacie RGB565), a szyna danych jest 8-bitowa, a więc aby przesłać jedną całkowitą ramkę obrazu wideo z kamery potrzebnych jest 76 800 x 2 = 153 600 taktów sygnału zegarowego PIXCLK. Oprócz sygnału zegarowego i 8-bitowej szyny danych występują jeszcze dwa sygnały synchronizujące, VSYNC (lub Frame_Valid) oraz HSYNC (lub Line_Valid). Pierwszy sygnał będąc w stanie aktywnym (wysoki poziom napięcia) informuje odbiornik, że w danej chwili jest wysyłana ramka obrazu, ale dopiero drugi sygnał ostatecznie określa czy kolejne bajty na szynie danych powinny być odczytywane przy narastającym zboczu sygnału PIXCLK (lub opadającym w zależności od konfiguracji, rysunek 6 ).

Rys. 6. Przebiegi czasowe sygnałów interfejsu danych wideo

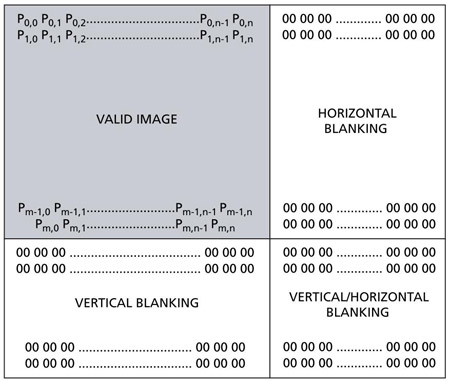

Czas trwania stanu aktywnego linii Line_Valid jest określony przez okres sygnału PIXCLK oraz liczbę kolumn wyjściowej matrycy pikseli razy dwa. W konkretnym przypadku, jeżeli częstotliwość wyjściowego sygnału zegarowego wynosi 25 MHz (okres = 40 ns), to przesłanie 320 pikseli (640 bajtów) jednego wiersza zajmie 25,6 us, a ponieważ wierszy w matrycy jest 240 to przesłanie całej ramki zajmie 6,144 ms. W rzeczywistości jednak pomiędzy stanem aktywnym zarówno sygnału Line_Valid jak i Frame_Valid występują przedziały czasowe zwane Horizontal Blanking oraz Vertical Blanking odpowiednio. Służą one nie tylko po to by zmniejszyć częstotliwość wychodzących z kamery ramek obrazu, ale również dają pewien okres czasu na przetworzenie przez czujnik danych z matrycy CMOS. Stąd też proces odczytu ramki wideo obrazowo można przedstawić jako czytanie właściwych danych oraz odczekiwanie przez okres w którym trwa Horizontal lub Vertical Blanking (rysunek 7).

Rys. 7. Odczyt obrazu z kamery

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485