SoCrates – nowatorski komputer embedded z SoC: dwurdzeniowy Cortex-A9 i FPGA

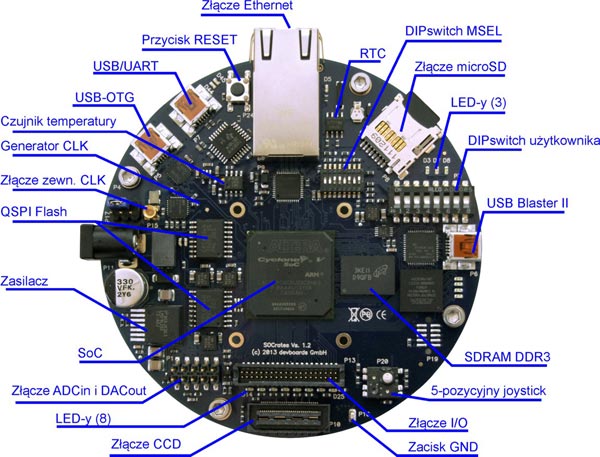

Otoczenie układu SoC w prezentowanym zestawie przypomina klasyczne systemy mikroprocesorowe, w jego skład wchodzą m.in.: cyfrowy czujnik temperatury, zegar czasu rzeczywistego, 1 GB pamięci DDR3 (w konfiguracji 32-bitowej), interfejs Ethernet 1 Gb/s, 1 kanały USB-OTG 2.0, a także interfejsy komunikacyjne CAN, SPI, I2C oraz UART z konwersją na USB. Użytkownik ma do dyspozycji złącze TFT-TP, złącze kamery CCD z interfejsem LVDS, 5-pozycyjny joystick, łącznie 12 diod LED (z czego 11 do wykorzystania przez użytkownika), 46 linii GPIO przystosowanych do poziomów logicznych TTL-LV33 (w tym 16 z bloku HPS) oraz 32 linie GPIO mogące pracować z poziomami TTL-LV33 lub TTL-LV25.

|

Elementy wyposażenia zestawu SoCrates:

|

Schemat blokowy ilustrujący budowę zestawu SoCrates przedstawiono na rysunku 3. W konfiguracji sprzętowej zestawu przygotowanej przez producenta przewidziano możliwość konfiguracji matrycy FPGA za pomocą interfejsu USB Blaster lub z konfiguratora-pamięci Flash (QSPI), program dla części mikroprocesorowej (zazwyczaj system operacyjny Linux) może być ładowany z innych źródeł: karty microSD lub drugiej wbudowanej w zestaw pamięci QSPI Flash.

Rys. 3. Schemat blokowy zestawu SoCrates

Ciekawostką w wyposażeniu zestawu jest pamięć DDR3: producent użył produkowanych przez firmę Micron pamięci z serii MT41K256M32SLD (taktowane do 333,33 MHz, docelowo mają być stosowane pamięci taktowane do 400 MHz), które nie są rekomendowane do stosowania w nowych aplikacjach (o czym producent wyraźnie informuje w dokumentacji zestawu). W przypadku budowy własnego urządzenia bazującego na którymś z układów Cyclone V SoC należy więc ostrożnie podchodzić do schematów udostępnionych przez producenta zestawu SoCrates.

Fot. 4. Wygląd zestawu SoCrates i rozmieszczenia jego najważniejszych elementów (trzy złącza nie są widoczne – znajdują się pod spodem PCB zestawu)

Pozostałe elementy zastosowane przez konstruktorów prezentowanego zestawu nie dostarczają takich emocji: warstwę fizyczną interfejsu USB-OTG spełnia popularny układ TUSB1210 firmy Texas Instruments, który komunikuje się z logiką zaimplementowaną w SoC poprzez interfejs ULPI. Schemat elektryczny interfejsu USB-OTG zaimplementowanego w zestawie SoCrates pokazano na rysunku 5.

Rys. 5. Schemat elektryczny interfejsu USB-OTG zastosowanego w zesatwie SoCrates

Także w torze Ethernet zastosowano nowoczesne rozwiązanie: układ PEF7071 firmy Lantiq, który jako jeden z niewielu na rynku spełnia wymogi standardu IEEE 802.3az (energooszczędny standard interfejsu Ethernet). Układ ten komunikuje się z logiką zaimplementowaną w SoC za pomocą interfejsu RGMII v1.3 oraz v2.0 MAC z mechanizmem kompensacji opóźnień w transmisji danych (RGMII-ID).

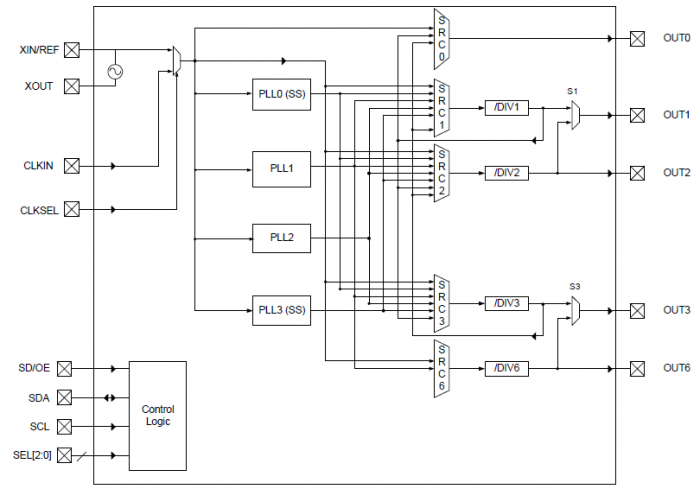

W interesujący sposób konstruktorzy zestawu rozwiązali taktowanie systemu wbudowanego w układ SoC i współpracujące z nim peryferia. Rolę generatora taktującego spełnia 7-kanałowy, programowany generator-syntezer częstotliwości o nazwie 5V49EE904, produkowany przez firmę IDT. Ma on wbudowane 4 pętle PLL, z których jedna może być programowana współczynnikami o wartościach ułamkowych, a także system multiplekserów i preskalerów widocznych na schemacie blokowym na rysunku 6.

Rys. 6. Schemat blokowy 7-kanałowego, programowanego syntezera częstotliwości 5V49EE904

Kanały generatora taktującego mogą być programowane przez użytkownika (poprzez interfejs I2C), linie wyjściowe mogą pracować z programowanymi prędkościami narastania sygnałów, są one zgodne ze standardami LV-TTL33, LVCMOS33, LVPECL, LVDS oraz HCSL. Sygnały zegarowe są wytwarzane na bazie rezonatora wbudowanego w płytkę, dopuszczalne jest także wykorzystanie zewnętrznego sygnału taktującego, który można podać na gniazdo P15 (rysunek 7).

Rys. 7. Schemat elektryczny generatora sygnałów taktujących z etykietami opisującymi zastosowanie poszczególnych linii CLK

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485