W kolejnej części kursu przedstawiamy prosty IP Core przeznaczony do sterowania 7-segmentowym wyświetlaczem LED…

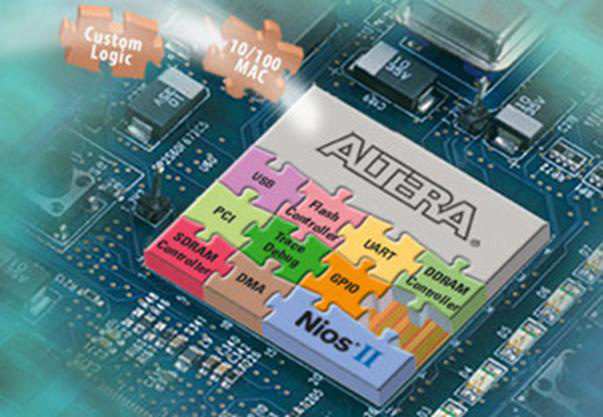

Altera MAX10 – przyjazne FPGA z bezpłatnym środowiskiem projektowym

Układy FPGA z rodziny MAX10 są tanimi platformami sprzętowymi o cechach układów SoC (System-on-Chip), w których – dzięki dużym i przemyślanym zasobom logicznym – można zintegrować nie tylko własną „logikę” ale także kompletny 32-bitowy mikrokontroler…

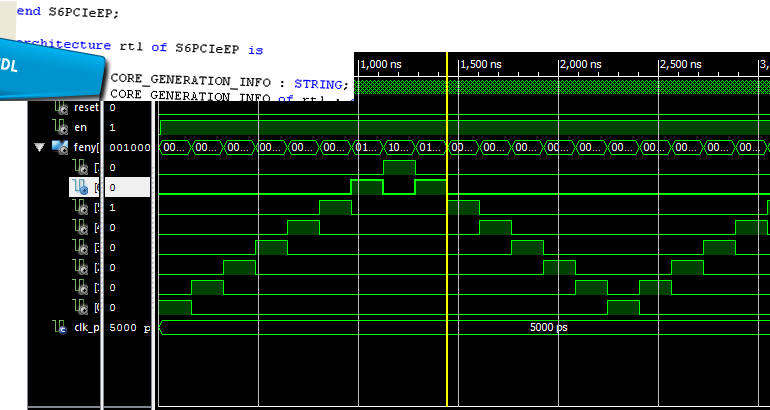

[KURS FPGA 12] Obsługa 2-cyfrowego wyświetlacza LED

W kolejnym odcinku kursu przedstawiamy sposób realizacji sterownika multipleksowego 2-pozycyjnego wyświetlacza LED…

[KURS FPGA 11] Jak zbudować dekoder wyświetlacza 7-segmentowego

W kolejnym odcinku kursu projektowania FPGA pokazujemy sposób użycia kolejnego przydatnego mechanizmu języka VHDL – deklaracji stałych (tablic)…

Altera w rękach firmy Intel

Firmy Intel Corporation i Altera Corporation poinformowały o zawarciu porozumienia, na mocy którego Intel kupi Alterę. Łączny koszt transakcji wyniesie 16.7 mld USD.

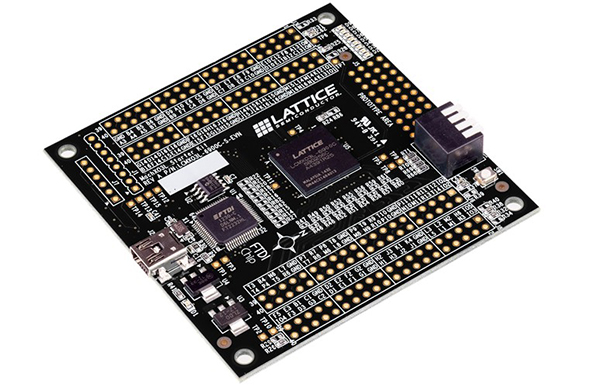

Niedrogi zestaw z układem programowalnym Lattice Semiconductor MachXO3L

W cenie około 25 USD firma Lattice Semiconductor oferuje kompletną platformę z układem programowalnym MachXO3L.

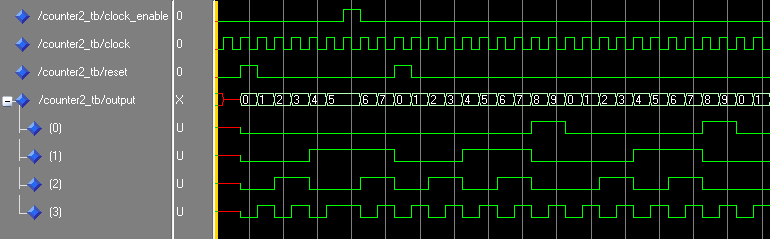

[KURS FPGA 10] Projektowanie liczników

W kolejnej części kursu zajmujemy się – na przykładzie licznika – opisem bloków synchronicznych.

Lattice Semiconductor oferuje energooszczędne rozwiązanie rozpoznające mowę

System wykrywania głosu ludzkiego i poleceń mieści się w programowalnym układzie o wymiarach 2,1 x 2,1 mm i zużywa około jednej trzeciej mocy w stosunku do konkurencyjnych rozwiązań.

[PRZEDŁUŻONY TERMIN] Europejski konkurs dla konstruktorów „Digilent Design Contest”

Jeżeli interesujesz się mikrokontrolerami lub FPGA i chcesz spróbować swoich sił na arenie międzynarodowej – to jest konkurs dla Ciebie! W notatce przedstawiamy szczegółowe informacje o konkursie organizowanym przez firmę Digilent…

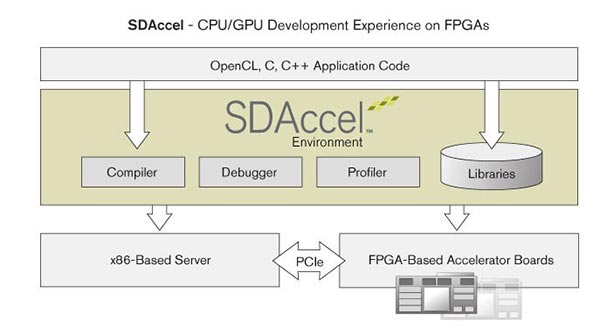

SDAccel – nowe środowisko projektowe Xilinx dla układów FPGA

Firma Xilinx ogłosiła wprowadzenie na rynek środowiska programistycznego SDAccel, przeznaczonego do pracy z układami FPGA przy użyciu języków C, C++ oraz frameworku OpenCL.