Wykorzystywanie trybów pracy o obniżonym poborze energii w mikrokontrolerach NXP LPC1700

Dodatkowe porady pozwalające zmniejszyć pobór energii

W mikrokontrolerach rodziny LPC1700 zużycie energii można dodatkowo obniżyć rozpatrując następujące obszary: częstotliwość taktowania CPU, rejestr wyboru zegara peryferiów (PCLKSEL0/1), rejestr sterujący zasilaniem peryferiów (PCONP) i inne.

Częstotliwość taktowania CPU

W mikrokontrolerach LPC1700 częstotliwość taktowania CPU można wybierać poprzez zmianę źródła sygnału zegarowego, konfigurację pętli PLL i/lub zmianę wartości podziału częstotliwości zegara CPU. Pozwala to na ustalanie kompromisu między szybkością działania, a obniżaniem poboru energii, w zależności od wymagań danego projektu. Obniżenie częstotliwości wyjściowej pętli PLL0 (FCCO, od 275 do 550 MHz) także może poskutkować redukcją poboru energii.

Ośmiobitowy dzielnik częstotliwości zegara CPU daje szeroką gamę opcji, w tym możliwość okresowego spowolnienia pracy CPU, dającego oszczędności energetyczne, bez konieczności wyłączania pętli PLL0.

Rejestr wyboru zegara peryferiów (PCLKSEL0/1)

Częstotliwość sygnału zegarowego taktującego dane peryferium ustala para bitów w rejestrze wyboru zegara peryferiów (Peripherial Clock Selection, PCLKSEL) (rysunek 9). W zależności od wymagań projektu, użytkownik może wykorzystać rejestry PCLKSEL0/1 do obniżenia częstotliwości zegara danego peryferium, obniżając tym samym pobór energii. Szczegóły dotyczące tego tematu można znaleźć w podręczniku użytkownika układów rodziny LPC17xx (LPC17xx User Manual).

Rejestr sterujący zasilaniem peryferiów (PCONP)

Rejestr sterujący zasilaniem peryferiów (Peripherial Power Control Register, PCONP) zawiera bity sterujące włączające i wyłączające pojedyncze peryferia. Pozwalają one na eliminację zużycia energii przez peryferia, które nie są potrzebne poprzez wyłączenie ich. Każdy z bitów w rejestrze PCONP odpowiada jednemu peryferium. Jeśli jest ustawiony na 1, jest ono włączone. Jeśli jest ustawiony na 0, zegar tego peryferium jest odłączany. Dla przykładu, jeśli bit numer 19 jest ustawiony na 1, włączony jest interfejs I2C1. Z kolei jeśli jest ustawiony na 0, interfejs ten jest wyłączony. Warto zauważyć, że poprawny odczyt z rejestru peryferium oraz zapis do niego jest możliwy tylko jeśli dane peryferium jest włączone w rejestrze PCONP. Szczegóły dotyczące tego tematu można znaleźć w dokumencie LPC17xx User Manual.

Inne

Akcelerator pamięci Flash

Jeśli wykonywany program jest zapisany we wbudowanej pamięci Flash, warto włączyć akcelerator tej pamięci. Włączenie go pozwala na wykorzystanie kilku dodatkowych buforów i ogranicza liczbę odwołań do pamięci, zmniejszając tym samym pobór energii.

Wykrywanie spadku napięcia (Brown-Out Detect)

Układ wykrywania spadku napięcia (Brown-Out Detect, BOD) jest domyślnie włączony i może zwiększyć prąd statyczny (w trybach Deep-sleep i Power-down) o 40 µA. Jeśli BOD nie jest potrzebny, można go wyłączyć w rejestrze PCON (rysunek 3).

Oprogramowanie

Większość programów dla systemów wbudowanych zawiera nieskończoną pętlę while(1) i w razie potrzeby obsługuje przerwania. W takim rozwiązaniu kod jest nieustannie pobierany z wbudowanej pamięci Flash i wykonywany, co zwiększa zużycie energii. Lepszym rozwiązaniem jest przełączenie układu w tryb uśpienia i oczekiwanie na przerwania od peryferiów, które wybudzają procesor. Można w ten sposób osiągnąć zauważalne oszczędności energetyczne.

Dzielnik zegara USB

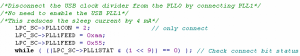

W mikrokontrolerach LPC1700 zastosowany został dzielnik częstotliwości zegara USB (rysunek 9), służący do wytwarzania sygnału taktującego USB z sygnału wyjściowego pętli PLL0, gdy pętla PLL1 (przeznaczona do generacji zegara USB) nie jest używana. Jeśli PLL1 nie jest wykorzystywana, sygnał pllclk jest ciągle podawany na dzielnik częstotliwości zegara USB, co zwiększa prąd dynamiczny o 5 do 7 mA. Użytkownik może odłączyć dzielnik częstotliwości zegara USB od sygnału pllclk włączając pętlę PLL1. Nie jest to jednak konieczne. Poniższy fragment kodu pokazuje, jak odłączyć dzielnik częstotliwości zegara USB od sygnału pllclk. Jest to przydatne w systemach, w których interfejs USB nie jest wykorzystywany.

Rys. 10. Przykład kodu odłączającego dzielnik częstotliwości zegara USB od sygnału pllclk

Wyprowadzenia portów I/O

Użytkownik może podjąć kroki prowadzące do dalszego obniżenia zużycia prądu na szynie 3,3 V (VDD(3V3) – napięcie zasilania dla portów I/O) przy pracy w trybach pracy o obniżonym poborze energii. Wszystkie wyprowadzenia portów ogólnego przeznaczenia (GPIO) w układach rodziny LPC1700 mają programowalne wewnętrzne podciągnięcie napięcia. Przed wejściem w tryb pracy o obniżonym poborze energii użytkownik może ograniczyć prąd źródła VDD(3V3) w następujący sposób:

1. Wszystkie wyprowadzenia I/O ogólnego przeznaczenia (GPIO) mają domyślnie podłączony rezystor podciągający. Używając rejestrów PINMODEx należy najpierw wyłączyć wewnętrzne podciąganie napięcia na wyprowadzeniach wszystkich portów. Następnie należy skonfigurować wyprowadzenia jako wyjścia GPIO i ustawić w stan niski.

ALBO

2. Używając rejestrów PINMODEx należy najpierw wyłączyć wewnętrzne podciągnięcia na wszystkich wyprowadzeniach. Następnie należy skonfigurować wyprowadzenia jako wejścia GPIO i przy pomocy zewnętrznego rezystora podciągnąć je do poziomu wysokiego lub niskiego.

3. Używając zewnętrznego rezystora należy ustawić pin TCK (JTAG Test Clock) w stan niski. Jeśli wyprowadzenie to jest pozostawione bez dołączenia i „pływa”, zużycie prądu wzrasta o 40 µA.

Warto zwrócić uwagę na to, że w trybie Deep Power-down stan wyprowadzeń portów I/O nie wpływa na zużycie prądu i wymienione powyżej zabiegi nie są konieczne.

Informacje o debugowaniu

Użytkownik powinien być świadomy pewnych ograniczeń występujących podczas debugowania. Najważniejszym z nich jest fakt, że mikrokontrolery LPC17xx nie mogą zostać wybudzone z trybów Deep-sleep oraz Power-down podczas pracy i zalecane jest nie używanie tych trybów podczas debugowania. Wybudzenie z trybów Deep-sleep i Power-down przebiega następująco. Gdy układ zostanie zaprogramowany przez interfejs JTAG/SWD, kabel USB do debugera JTAG/SWD (np. Keil ULINK2) należy odłączyć od programowanego systemu a następnie wykonać restart poprzez odłączenie i powtórne podłączenie zasilania.

Następną kwestią jest to, że w trybie debugowania zmienia się sposób obsługi trybów pracy o obniżonym poborze energii przez rdzeń Cortex-M3. Powoduje to, że w czasie debugowania tryby te funkcjonują inaczej niż w trakcie normalnej pracy. Występujące różnice powodują, że pomiary zużycia energii powinny być przeprowadzane w czasie normalnej pracy systemu, a nie przy debugowaniu, kiedy to wyniki są zawyżone.

Demonstracja wykorzystania trybów pracy o obniżonym poborze energii

Wymagania

Sprzęt

Wykorzystywana jest płytka Keil MCB1700 (przedstawiona na rysunku 11), interfejs JTAG Keil ULINK2 oraz kabel RS-232.

Uwaga: Zamiast Keil ULINK2, do programowania płytki LPC1700 można użyć kabla RS-232 wraz z narzędziem FlashMagic, dostępnym bezpłatnie na stronie internetowej firmy NXP.

Oprogramowanie

Używane jest środowisko Keil uVision4 (do uruchomienia prezentowanego tu programu wystarcza wersja ewaluacyjna). Program demonstracyjny jest zgodny z CMSIS (Cortex Microcontroller Software Interface Standard). Do wyświetlenia opcji wchodzenia w tryby pracy o obniżonym poborze energii konieczne jest okno TeraTerm lub HyperTerminal.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485