Renesas Synergy – zintegrowana platforma sprzętowo-programowa dla aplikacji IoT

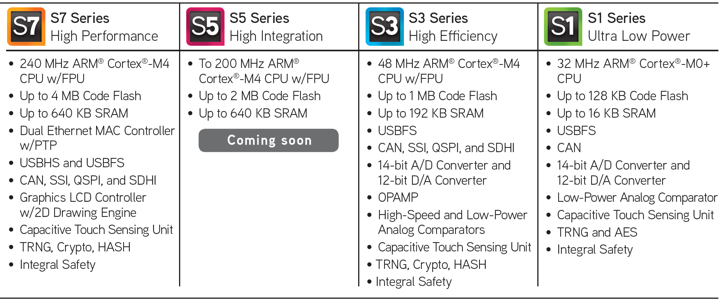

Tab. 1. Zestawienie najważniejszych cech poszczególnych rodzin mikrokontrolerów Renesas Synergy

Zestawienie najważniejszych cech produkowanych i przygotowywanych do wdrożenia do produkcji mikrokontrolerów z rodziny Synergy przedstawiono w tabeli 1. Jak widać, bazowym dla firmy Renesas rdzeniem z rodziny Cortex-M jest model M4F (zintegrowany w koprocesorem zmiennoprzecinkowym FPU), który w zależności od rodziny może być taktowany z maksymalną częstotliwością 48/200/240 MHz. Dla aplikacji o szczególnie dużych wymaganiach dotyczących poboru energii, firma Renesas przygotowała rodzinę mikrokontrolerów Synergy S1, które wyposażono w rdzeń Cortex-M0+ przystosowany do taktowania sygnałem zegarowym o częstotliwości do 32 MHz.

|

Renesas Synergy Gallery

Firma Renesas przygotowała specjalny portal, który jest centrum supportowo-dystrybucyjnym dla użytkowników platformy Synergy. Jest on dostępny pod adresem: www.renesassynergy.com. W ramach zasobów tego portalu (Synergy Gallery, dostępna bezpośrednio pod adresem synergygallery.renesas.com) są dostępne – na razie jeszcze w niewielkiej liczbie – przykładowe projekty oraz dodatkowe biblioteki i specyficzne drivery, które producent podzielił na dwie grupy: weryfikowane (przystosowane do pracy na wszystkich platformach Synergy) i kwalifikowane, które spełniają wszystkie formalne wymogi kompatybilność z SSP, ale bez szczegółowego monitorowania i testowania zmian w kolejnych wydaniach oprogramowania. |

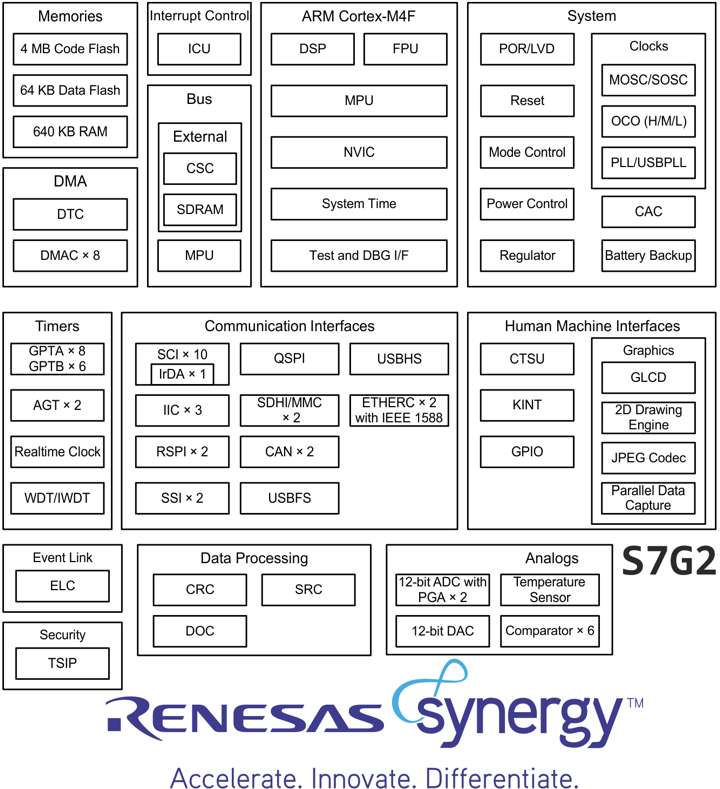

Wyposażenie poszczególnych rodzin mikrokontrolerów producent zróżnicował, tworząc platformy sprzętowe optymalizowane dla różnych aplikacji docelowych. Zróżnicowanie dotyczy nie tylko liczby i funkcji wbudowanych bloków peryferyjnych, ale także pojemności wewnętrznych pamięci Flash i RAM, które mogą wynosić od maksimum 128 kB do 4 MB (Flash) i od 16 kB do 640 kB (RAM). Ogólny schemat blokowy mikrokontrolerów S7G2, pozwalający zorientować się co do ich wyposażenia wewnętrznego, pokazano na rysunku 2.

Rys. 2. Ogólny schemat blokowy mikrokontrolerów S7G2

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485