Chipathon SSCS PICO 2026 – konkurs na projekt układu scalonego typu open source

Stowarzyszenie IEEE Solid-State Circuits Society (SSCS) ogłosiło kolejną edycję konkursu na projekt układu scalonego (IC) typu open source, organizowanego w ramach programu PICO (Platform for IC Design Outreach).

Inicjatywa OpenROAD sponsoruje Chipathon, realizując swoją misję wspierania i wzmacniania ekosystemu OpenEDA. Wydarzenie jest otwarte dla wszystkich (bez ograniczeń). Do udziału zaproszeni są uczniowie szkół średnich, studenci oraz osoby z regionów niedostatecznie reprezentowanych w społeczności projektantów układów scalonych.

Tegoroczny konkurs SSCS PICO Open-Source Chipathon zakończy się specjalnymi warsztatami, podczas których zespoły zaprezentują swoje projekty, wnioski oraz, w miarę możliwości, wyniki pomiarów krzemowych w formie wykładów, plakatów i pokazów. Warsztaty będą kładły nacisk na powtarzalność, modułowe elementy open-source oraz przejrzystą ocenę (artefakty weryfikacyjne i wskaźniki porównawcze), a także będą oferowały możliwość opublikowania artykułu w związku z warsztatami.

Celem tego chipathonu jest wspieranie współpracy oraz przyspieszenie tworzenia gotowych do ponownego wykorzystania, otwartych komponentów układów scalonych oraz narzędzi, z myślą o stworzeniu otwartego zestawu PDK (GF180MCUD). Zespoły będą wspierane przez doświadczonych mentorów i przejdą przez cały proces – od specyfikacji aż po materiały gotowe do produkcji.

Zarys konkursu (struktura etapowa)

Rejestracja do 1 maja 2026 r.

- Etap 1 (maj): Wprowadzenie + cotygodniowe sesje szkoleniowe + prezentacje projektów; utworzenie zespołów do końca etapu 1.

- Etap 2 (maj/czerwiec): Realizacja pod okiem mentorów, konfiguracja narzędzi, procesy projektowe, metodologia oraz spełnienie specyfikacji projektowych.

- Faza 3 (lipiec): Formalne przeglądy projektów dla każdego zespołu; opinie ekspertów.

- Faza 4 (sierpień/wrzesień): Ostateczna weryfikacja i integracja; czysty DRC/LVS oraz przesłanie pakietu do tapeoutu przed upływem terminu.

- Faza 5 (po tapeoucie): Uruchomienie układów scalonych i pomiary (tam, gdzie dostępne są odpowiednie urządzenia); wyniki dodane do otwartych repozytoriów.

- Przesłanie dokumentacji końcowej

Ścieżki i praca w zespołach pod okiem mentorów-wolontariuszy

Ścieżka A — Podstawowe elementy składowe

Bloki IP i infrastruktury wielokrotnego użytku (analogowe/mieszane i cyfrowe), które mają szerokie zastosowanie w wielu układach scalonych. Tworzenie bloków cyfrowych przy użyciu zestawu narzędzi OpenROAD dla przepływu RTL-GDS, wraz z innymi narzędziami do charakteryzacji bibliotek, narzędziami cyfrowymi i AMS. Obejmują one bloki takie jak sumatory, bloki ścieżki danych DSP, mikrokontrolery, automaty skończone (FSM) itp. Podstawowe obwody analogowe i mieszane oraz makra, np. odniesienie Bandgap (BGR) ze źródłem prądu ZTAT/PTAT, oscylator pierścieniowy (ewentualnie z kompensacją temperatury), 8-bitowy przetwornik analogowo-cyfrowy SAR, 8-bitowy przetwornik cyfrowo-analogowy sterujący prądem, wzmacniacze, bloki pamięci), z naciskiem na solidną weryfikację i możliwość ponownego wykorzystania.

Liderzy: James Stine, Saroj, Gaurav, Akhilesh Patil, Sumanth Kamineni

Ścieżka B — Układy dla czujników

Opracowywanie analogowych/mieszanych układów przedwzmacniających oraz układów przetwarzania brzegowego do zastosowań takich jak monitorowanie jakości wody, wykrywanie parametrów środowiskowych, opieka zdrowotna i inteligentna infrastruktura, ze szczególnym uwzględnieniem kompaktowych, autonomicznych systemów. Zbliżamy się do podejścia opartego na chipletach, w którym obwody mikroelektroniczne są projektowane jako interfejsy dla rozproszonych, natywnych dla brzegów systemów, które integrują MEMS, czujniki chemiczne/biologiczne i CMOS, aby umożliwić rzadkie, sterowane zdarzeniami wykrywanie, przetwarzanie w czujniku i TinyML na brzegach — a wszystko to przy ultra niskim zużyciu energii.

Liderzy: Camilo Velez, Vipul Sharma,

Ścieżka C — MOSbius – plac zabaw dla chipów

Projekty typu „uczenie się poprzez pomiary” (chipy w stylu MOSbius) skoncentrowane na szerokiej dostępności i praktycznej nauce. Możliwość włączenia automatyzacji.

Liderzy: Peter Kinget, Juan Moya Baquero, Luighi

Ścieżka D — Układy wspomagane przez sztuczną inteligencję i duże modele językowe

Ten tor skupia się na procesach pracy wspomaganych przez AI/LLM, służących do opracowywania gotowych do produkcji układów analogowych i cyfrowych. Tematyka obejmuje agentowe procesy projektowe, metodologie oparte na generatorach, eksplorację przestrzeni projektowej oraz powtarzalne podejścia do projektowania analogowego i niestandardowego. Projekty powinny prezentować praktyczne metody wspomagane przez AI, które przyspieszają i automatyzują proces projektowania układów scalonych, od specyfikacji i eksploracji architektury po generowanie RTL, implementację obwodów, projektowanie fizyczne, weryfikację i zamknięcie, a wszystko to w celu uzyskania wyników gotowych do produkcji.

Liderzy: Luighi, Mehdi Saligane, Saptarshi Ghosh, Gaurav, Osama Khan, Trio Adiono/Nur, Mauricio Montanares

Komisja ds. narzędzi i procesów referencyjnych: Mitch, Harald, Leo, Saroj, Mehdi, Peter, Vipul, Herman, Luighi

Oczekiwane wyniki

W terminie zakończenia projektowania każdy zespół powinien dostarczyć:

- Repozytorium umożliwiające odtworzenie projektu (open source), zawierające:

- Specyfikacje, dokumentację projektową oraz listę kontrolną weryfikacji

- Listy sieciowe/układ (lub skrypty generujące), środowiska testowe oraz wyniki symulacji

- Bazę danych bloku (lub zintegrowanego makra) zgodną z DRC/LVS

- Materiały integracyjne wymagane przez szablon na poziomie układu scalonego (szczegóły przekazane w trakcie programu)

Po otrzymaniu próbek krzemu (jeśli to możliwe):

- Notatki dotyczące uruchomienia, plan pomiarów, wyniki pomiarów oraz film demonstracyjny dodane z powrotem do repozytorium projektu

Wyniki oraz wyprodukowane układy scalone zostaną zaprezentowane w wybranym medium.

Kwalifikowalność, koszty i udział

- Otwarte dla wszystkich uczestników z całego świata (bez ograniczeń).

- Uczestnictwo obejmuje cotygodniowe spotkania i okresowe przeglądy.

- Nie jest wymagane wcześniejsze doświadczenie w zakresie tapeoutu; organizatorzy zapewniają mentoring; chipathon nie jest szkoleniem ani kursem.

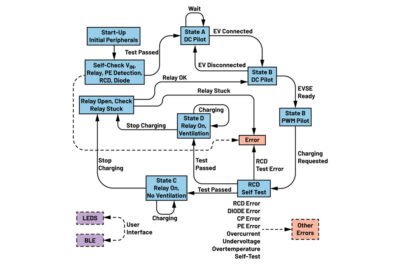

Projektowanie układów IC-CPD: Podstawowe wytyczne dotyczące sprzętu i oprogramowania dla urządzeń sterowania i zabezpieczeń wbudowanych w kabel ładowania

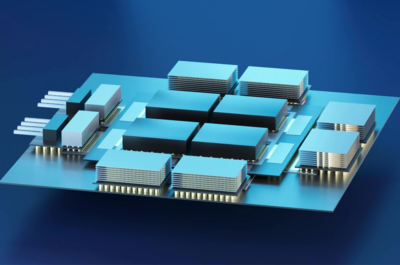

Projektowanie układów IC-CPD: Podstawowe wytyczne dotyczące sprzętu i oprogramowania dla urządzeń sterowania i zabezpieczeń wbudowanych w kabel ładowania  NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W

NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W  Europractice 2.0 – usługi projektowania i prototypowania chipów – finansowane przez UE do września 2028 r.

Europractice 2.0 – usługi projektowania i prototypowania chipów – finansowane przez UE do września 2028 r.