Prosty projekt w VHDL dla CPLD firmy Xilinx z rodziny CoolRunner

Schemat blokowy urządzenia przedstawiono na rysunku 2, który zawiera podział na funkcjonalne bloki. Należy tu wymienić następujące elementy:

- dzielnik częstotliwości,

- licznik modulo 4,

- multiplekser wejściowy MUX1,

- multiplekser sterujący wyświetlaczem MUX2,

- dekoder

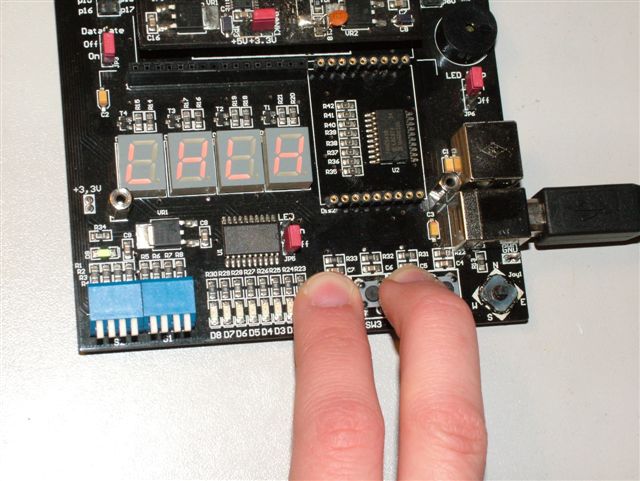

Fot. 3. Zestaw ZL14PLD + ZL15PLD po zaprogramowaniu CPLD

Naciśnięcie przycisku przyłączonego do wejścia Reset powoduje wymuszenie określonego stanu początkowego (w tym projekcie sprowadza się to do wyzerowania wszystkich liczników). Częstotliwość wejściowego sygnału zegarowego doprowadzonego do wejścia Clk jest wstępnie podzielona przez dzielnik częstotliwości. Zbudowany on jest w oparciu o binarny licznik synchroniczny.

Fot. 4. Zestaw ZL14PLD + ZL15PLD w akcji

Do poprawnego sterowania wyświetlaczem w trybie multipleksowanym konieczne jest włączanie poszczególnych cyfr z odpowiednią prędkością. By otrzymać finalnie zbliżoną częstotliwość przełączania cyfr w wyświetlaczu wymaga to użycia różnego stopnia podziału częstotliwości we wstępnym dzielniku. Uzyskany nowy wewnętrzny sygnał zegarowy (DClk) jest doprowadzony do dwubitowego licznika. Jego stan (SelCnt) pozwala na rozróżnienie czterech stanów i jest doprowadzony do multipleksera wejściowego oraz dekodera wyjściowego. W zależności od stanu tego licznika poprzez multiplekser MUX1 na linię KeyIn przesłany jest stan jednego z czterech przycisków (KeyIn0…KeyIn3). Stan logiczny sygnału KeyIn steruje włączaniem poszczególnych segmentów w wyświetlaczu LED, które jest zrealizowane w oparciu o multiplekser (właściwie jest to ośmiobitowy multiplekser z jedną linia sterującą). Ze względu na wyświetlanie jednego z dwóch możliwych znaków na wyświetlaczu układ sterujący włączaniem poszczególnych segmentów jest funkcją kombinacyjną zbudowaną w oparciu o multiplekser z jednobitową informacją adresową.

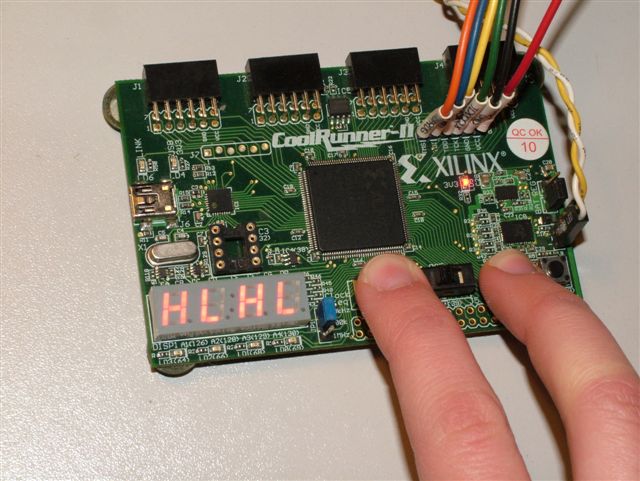

Fot. 5. Zestaw SK-CRII-L-G firmy DIGILENT po zaprogramowaniu CPLD

Stałe doprowadzone do wejść multipleksera (0111000 i 1110110) są tak dobrane by na wyświetlaczu zobrazowany był znak H lub L w zależności od tego, czy dany przycisk jest naciśnięty czy nie. Synchronicznie z multiplekserem wejściowym pracuje dekoder wyjściowy. Jego zadaniem jest wygenerowanie właściwych sygnałów włączających odpowiednie cyfry wyświetlacza. Realizacja dekodera opiera się o zbiór (czterech) funkcji kombinacyjnych, których rezultaty są doprowadzone do wyjść układu CPLD (DSel0 .. DSel3). W zależności od zestawu uruchomieniowego ich implementacja jest odmienna, gdyż musi uwzględniać specyfikę danego zestawu. Istotnym jest to, by w chwili gdy multiplekser wejściowy wybiera określony sygnał wejściowy (KeyIn0…KeyIn3), dekoder wyjściowy generował sygnał włączeniem odpowiedniej cyfry. W momencie, gdy stan licznika modulo 4, adresuje przykładowo sygnał z wejścia KeyIn0, dekoder wyjściowy włącza cyfrę DSel0.

Fot. 6. Zestaw SK-CRII-L-G firmy DIGILENT w akcji

Ogólnie wiadomo, że przy współpracy układów cyfrowych z elementami stykowymi jakimi są przyciski zachodzi niekorzystne zjawisko dzwonienia styków w momencie ich przyciśnięcia lub zwolnienia. W przedstawionym projekcie zjawisko to zostało całkowicie zignorowane. Analizując realizację projektu można zauważyć, że występujące drgania styków w momentach przełączania nie wpływają w widoczny sposób na działanie urządzenia.

Po zaprogramowaniu układów CPLD można sprawdzić działanie urządzenia.

Andrzej Pawluczuk

Autoryzowanym dystrybutorem firmy Digilent w Polsce jest Kamami, ul. Lwowska 5, 05-120 Legionowo, http://www.kamami.pl.

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)  Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku

Analiza rynku sztucznej inteligencji: firmy o największym wzroście przychodów z AI w 2026 roku  I-7520 – izolowany konwerter RS-232/RS-485

I-7520 – izolowany konwerter RS-232/RS-485