Czy można zdobyć kompetencje w projektowaniu układów scalonych korzystając z narzędzi open source? – na to pytanie odpowiada Krzysztof Herman z IHP

Dr Krzysztof Herman od trzech lat zajmuje się badaniami i rozwojem systemów półprzewodnikowych oraz technologii ultra wysokich częstotliwości w Leibniz Institute for High Performance Microelectronics (IHP) we Frankfurcie nad Odrą. Pracuje jako asystent naukowy ds. rozwoju IHP-Open-PDK (Process Design Kit) – pierwszego w Europie, w pełni otwartego zestawu komponentów do projektowania układów scalonych w technologii 130 nm BiCMOS (Bipolar Complementary Metal-Oxide-Semiconductor).

Wcześniej, przez osiem lat, był nauczycielem akademickim na Uniwersytecie del Bío-Bío, gdzie razem ze studentami tworzył chipy w oparciu o rozwiązania open-source silicon. W naszej rozmowie podkreślał, jak bardzo zmienił się paradygmat projektowania chipów. Obecnie, mając biurko, komputer i dostęp do bezpłatnej bazy przyrządów półprzewodnikowych – takich jak tranzystory oraz inne komponenty od kilku dostawców open source – można tworzyć własne układy scalone i wysyłać prototypy do produkcji.

Dlatego chciałby rozpropagować ideę Open Source Silicon również w Polsce.

Dr Krzysztof Herman

– W Ameryce Południowej wiatry technologiczne nie wieją tak mocno jak pomiędzy Stanami Zjednoczonymi a Europą – wspomina dr Krzysztof Herman. – Trochę czasu zajęło mi odnalezienie się w nowej rzeczywistości. Na początku – jako akustyk z wiedzą elektronika – zajmowałem się przetwarzaniem sygnałów i budowałem akceleratory do formowania wiązki ultradźwiękowej na układach FPGA.

Potem pojawiła się możliwość współpracy z chilijskim oddziałem amerykańskiej firmy Synopsys, która tworzy oprogramowanie do projektowania układów scalonych i systemów elektronicznych (EDA – Electronic Design Automation) oraz organizuje szkolenia w tym zakresie. Pomyślałem więc, że zainicjuję podobną działalność edukacyjną na chilijskim uniwersytecie.– Licencja dla uczelni kosztowała wówczas 1500 USD. Był to rok 2020 – początek pandemii. Zorganizowałem serwer dedykowany do tych celów i razem ze studentami realizowaliśmy własny projekt. Cena obejmowała również dedykowane pomieszczenie, a komputery używane do projektowania nie mogły być wykorzystywane do innych celów. Podpisaliśmy NDA (Non-Disclosure Agreement) i musieliśmy przestrzegać wszelkich klauzul poufności. Do tamtej pory studenci mogli skorzystać z danych, zaprojektować chip, napisać pracę magisterską lub doktorską, a potem musieli „schować wszystko do szuflady”. Szkoda, bo przecież takie działania powinny być jawne i transparentne, żeby inni mogli się na ich podstawie uczyć i rozwijać własne projekty. Motywacją jest oczywiście dyplom, ale później – gdy młody człowiek opuszcza środowisko uniwersyteckie – chciałby projektować układy dla konkretnych zastosowań.

Leibniz Institute for High Performance Microelectronics (IHP) we Frankfurcie nad Odrą

– Do 2020 roku taka możliwość była blokowana przez barierę finansową, ponieważ licencja użytkowa na jedno stanowisko to wydatek rzędu 50 tys. USD rocznie. Jaki startup może sobie pozwolić na takie koszty narzędzi projektowych? Kolejny wydatek to bloki funkcjonalne, tzw. IP – przecież nikt nie chce tworzyć wszystkiego od zera – nie wspominając o dostępie do środków produkcji. Koszty były i nadal są ogromne.

– To się zmieniło, gdy powstał Open Source Silicon, którego celem jest udostępnienie schematów, narzędzi projektowych i specyfikacji sprzętowych – podobnie jak ma to miejsce w świecie oprogramowania. Firmy SkyWater Technology i GlobalFoundries udostępniły otwarte zestawy projektowe PDK (Process Design Kit) do projektowania układów scalonych w domenie publicznej, dzięki finansowaniu Google. My w IHP również dołożyliśmy swoją część – i od tego wszystko się zaczęło.

Jak wygląda projektowanie układów scalonych w open source?

– Dawniej – i chyba do dziś – propagowany jest mit, że projektowanie układów scalonych jest bardzo skomplikowane. W rzeczywistości wcale tak nie jest – podkreśla dr Krzysztof Herman – szczególnie w dojrzałych technologiach. Jeśli ktoś ma doświadczenie w projektowaniu PCB, poradzi sobie bardzo dobrze. To trochę tak, jakby przesiąść się z roweru miejskiego na rower górski – inne manewry, inny teren i sposób jazdy. Podobnie jest z projektowaniem funkcjonalnych struktur na krzemie. W ramach PDK dostępne są biblioteki, które stanowią pomost między skomplikowanym procesem wytwarzania układów półprzewodnikowych a projektantem, ułatwiając opracowanie własnego układu.

– Można to wyjaśnić na podstawie analogii do projektowania wnętrz. Tam również dostępne są bloki z meblami i innymi elementami wyposażenia. Program korzysta z zestawów od konkretnych producentów, a projektant aranżuje przestrzeń na ich podstawie. Podobnie jak na rynku mebli różni dostawcy oferują swoje kolekcje, tak w domenie technologicznej różne fabryki półprzewodników proponują rozwiązania charakterystyczne dla danego procesu. Kiedy projekt wnętrza – lub układu scalonego – jest gotowy, jego dokumentację można wysłać do wykonawcy.

A jakie są koszty wytworzenia?

– Co do zasady, to cena zależy od technologii, a im bardziej jest zaawansowana, tym większa cena, która waha się od kilku do kilkudziesięciu tysięcy USD za 1 mm2. Firmy oferujące dostęp do technologii w ramach paradygmatu open source każą sobie płacić odpowiednią kwotę za milimetr kwadratowy krzemu, przy czym w procesie SkyWater trzeba kupić minimum 10 mm2, w cenie 1500 USD za 1 mm2, co oznacza 15 tys. USD. W GlobalFoundries koszt jest mniejszy, bo 1 mm2 to 350 USD, ale trzeba kupić minimum 20 mm2.

– Nasza oferta, dedykowana do użytkowników open-source, zależy od procesu i wynosi odpowiednio: 2800 EUR w przypadku procesu SG13G2 (zawiera ultra szybkie tranzystory HBT) oraz 1500 EUR w przypadku procesu SG13CMOS5L (podstawowy CMOS 130 nm). Minimalna wielkość zamówienia to 0.8 mm2. [Red.: więcej informacji o inicjatywie Open-Silicon MPW można znaleźć tutaj]

Czyli płaci się za wyprodukowanie, a projekt jest za darmo?

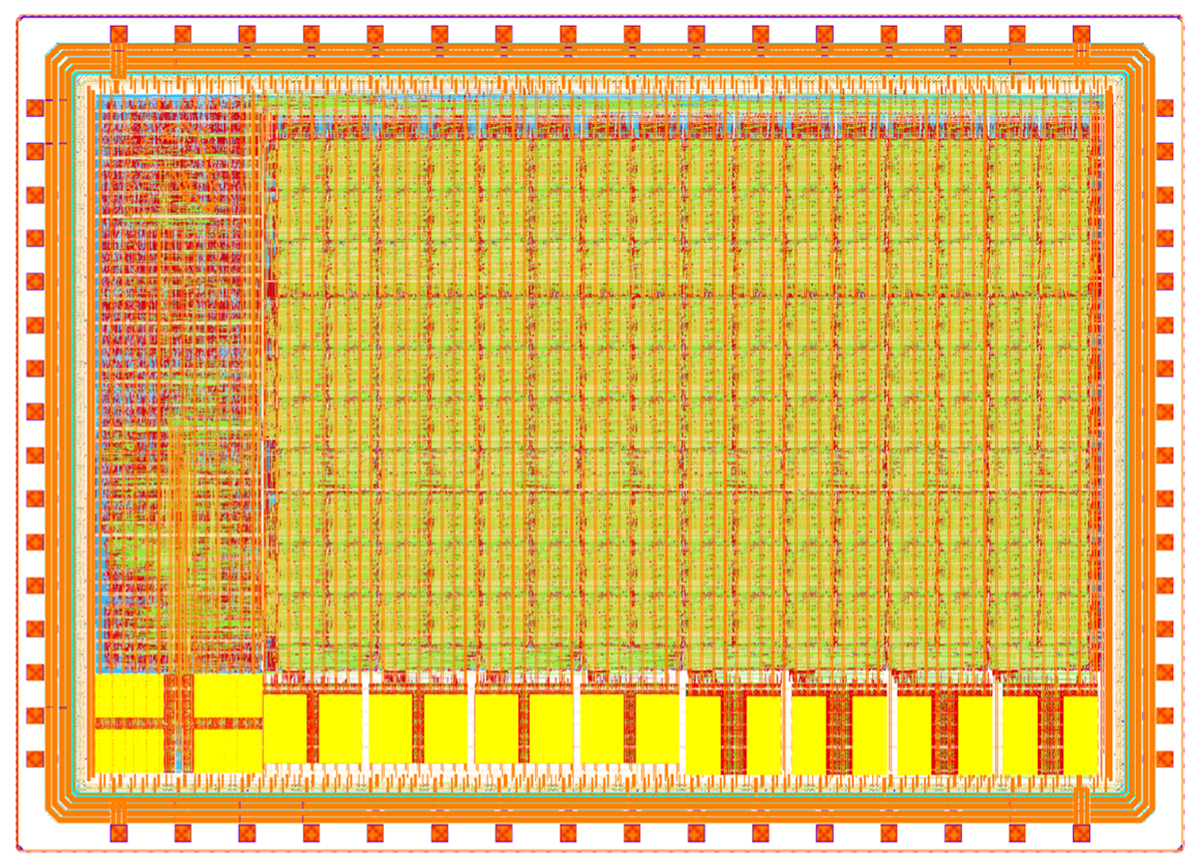

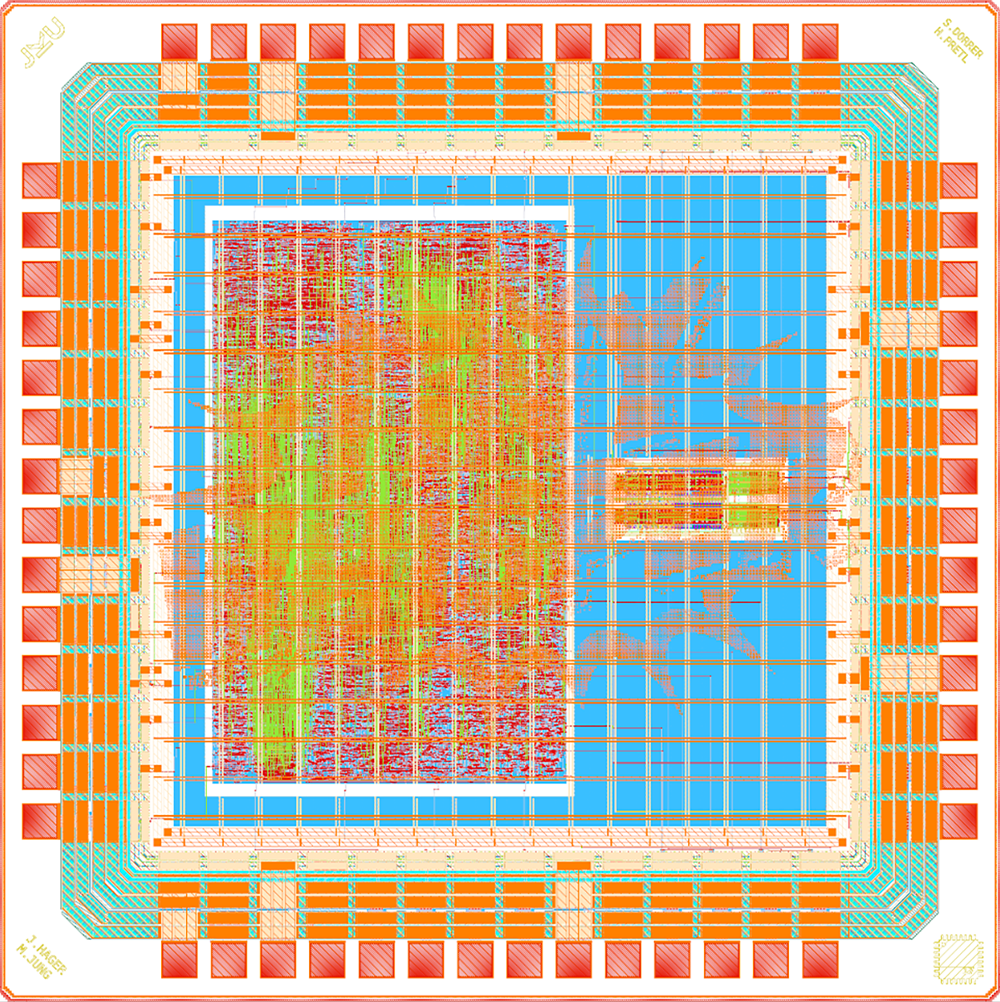

– W IHP przez dwa lata oferowaliśmy produkcję chipów za darmo. Podobnie SkyWater i GlobalFoundries – dzięki dofinansowaniu z Google. Dziś mamy około 100 wyprodukowanych układów, które obecnie mierzymy, aby sprawdzić, czy darmowe narzędzia EDA oraz nasz IHP-Open-PDK są rzeczywiście użyteczne.

– Na tę chwilę nasze doświadczenia są bardzo pozytywne – wszystkie przetestowane układy działają. Co ciekawe, są one dostępne dla każdego, kto chciałby je wypożyczyć do pomiarów lub testów. Warunkiem jest opublikowanie wyników na licencji open source oraz zwrot układu. Wszystkie projekty zostały wykonane przy użyciu narzędzi open-source EDA oraz naszego IHP-Open-PDK.

– Bariera dostępu do oprogramowania, technologii oraz środków produkcji została znacząco obniżona – zapewnia dr Krzysztof Herman. – Podobna rewolucja miała miejsce w przypadku Arduino czy STM, gdzie kursy oraz kody źródłowe udostępniane na licencjach open source zostały spopularyzowane na portalach i w repozytoriach takich jak GitHub. Obecnie można zaprojektować nawet skomplikowany system elektroniczny, korzystając z oprogramowania takiego jak KiCad, płacąc jedynie za materiały i produkcję. Dla przykładu – wytwarzanie nawet złożonych płytek PCB jest dziś możliwe w bardzo rozsądnych cenach. My chcemy powtórzyć ten schemat w domenie open-source silicon.

Jaką technologią dysponuje IHP?

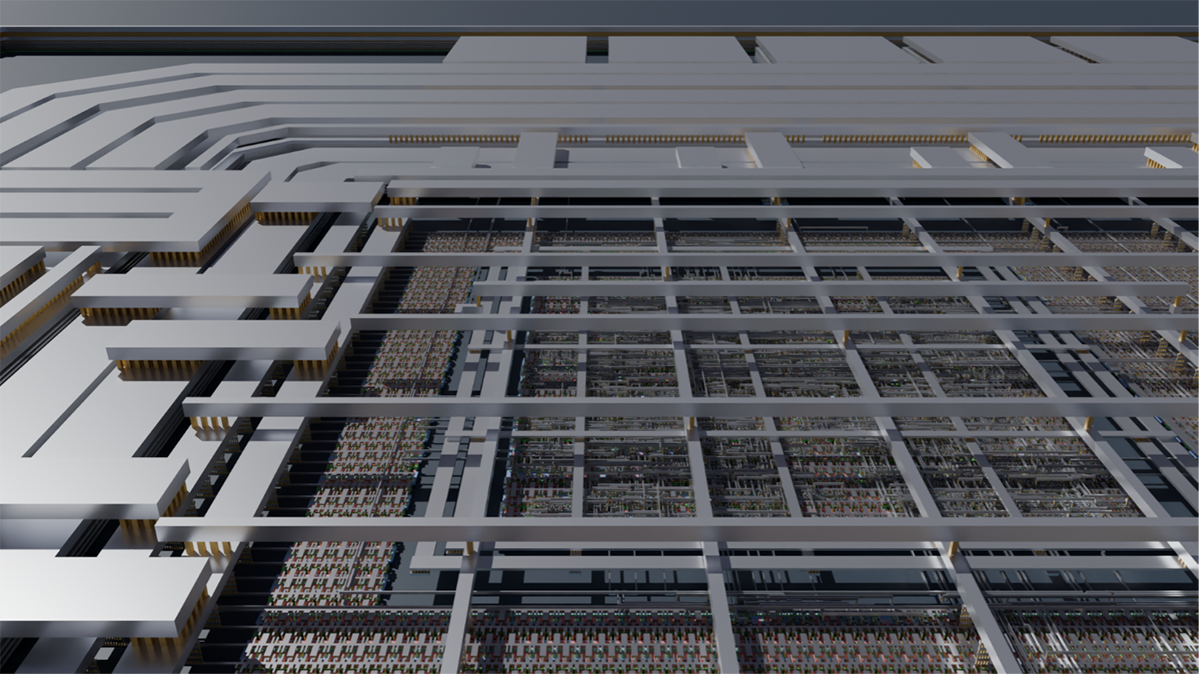

– IHP dysponuje linią produkcyjną 130 nm, operującą w oparciu o 8-calowe wafle krzemowe. Centralnym punktem możliwości produkcyjnych instytutu jest technologia krzemowo-germanowa, umożliwiająca wytwarzanie tranzystorów pracujących przy bardzo wysokich częstotliwościach, rzędu 600–700 GHz. Ta unikatowa technologia plasuje nas w ścisłej czołówce światowej w tym segmencie.

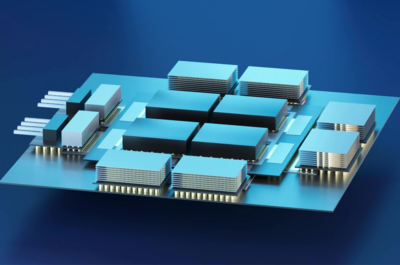

Nasz open-source PDK, oprócz ultraszybkich tranzystorów bipolarnych, oferuje również komplementarne tranzystory polowe (1,2 V oraz 3,3 V), rezystory, kondensatory MiM, waraktory, diody, elementy ESD oraz zestaw bloków funkcjonalnych do projektowania układów cyfrowych (standard cells, IO cells, SRAM).– Ze względu na to, że przyrządy CMOS są wykonane w technologii 130 nm, często pojawiają się pytania dotyczące ewentualnego unowocześnienia procesu. Odpowiedzią IHP jest heterointegracja, czyli scalanie wielu projektów wykonanych w różnych technologiach na jednym podłożu krzemowym. Pozwala to na integrację różnych technologii w mikroskali.

– Obecnie w IHP trwają prace nad rozwojem open-source ADK (Assembly Design Kit), który zapewni wsparcie dla projektantów chcących w pełni wykorzystać zalety różnych technologii. Równolegle opracowywane są również biblioteki open source dedykowane zastosowaniom kriogenicznym (Cryo), m.in. w systemach kwantowych, układom odpornym na promieniowanie (radiation hard), wykorzystywanym w aplikacjach kosmicznych, a także technologiom pamięci rezystywnej ReRAM. Wszystkie te działania znacząco rozszerzą zakres dostępnych zastosowań – podkreśla dr Krzysztof Herman.

Kto tworzy PDK oraz bloki IP?

– W IHP tworzeniem PDK oraz bloków IP zajmuje się dedykowany zespół, który został wzmocniony poprzez nowe rekrutacje w 2025 roku. Jego zadaniem jest rozwijanie modeli komponentów oferowanych w procesie technologicznym IHP, tak aby były one kompatybilne z narzędziami open-source EDA do projektowania układów scalonych.

– Równolegle IHP podejmuje działania mające na celu opracowanie biblioteki bloków IP dostępnych na licencji open source. Istnienie takiej biblioteki umożliwia projektantom tworzenie złożonych systemów w oparciu o istniejące i zweryfikowane moduły funkcjonalne. Projekt ten jest współfinansowany w ramach różnych inicjatyw, takich jak Joint Chips Undertaking, w których IHP pełni rolę jednego z liderów trzech wybranych konsorcjów. Naszym głównym obszarem odpowiedzialności jest rozwój części analogowo-mieszanej i RF (Analog Mixed-Signal RF). Pozostałe dwa konsorcja koncentrują się na rozwoju narzędzi open source do projektowania układów cyfrowych oraz na poprawie ich interoperacyjności.

– W perspektywie najbliższych 3–4 lat oczekujemy znaczącej poprawy funkcjonalności całego ekosystemu. Naszym celem jest przeniesienie narzędzi open source z poziomu akademickiego do zastosowań przemysłowych. Pracujemy także nad udostępnieniem otwartych narzędzi EDA, PDK oraz IP w ramach European Chip Design Platform „EuroCDP” — środowiska integrującego zarówno rozwiązania komercyjne, jak i bezpłatne.

– Już teraz w Europie działa kilka firm aktywnie zainteresowanych tym alternatywnym podejściem — podejmują one próby projektowania układów scalonych z użyciem darmowych narzędzi, a następnie poddają je procesowi weryfikacji. Eksploracja potencjalnych modeli biznesowych opartych na open-source silicon stanowi osobne, istotne zagadnienie.

A w jaki sposób można korzystać z PDK oraz biblioteki bloków IP?

– Nasz PDK jest dostępny publicznie na platformie GitHub. Udostępniamy także kursy oraz szablony projektowe dla układów analogowych i cyfrowych. Repozytoria z projektami układów, które zostały dotychczas wyprodukowane, również są dostępne dla każdego, kto chciałby się z nimi zapoznać. Narzędzia EDA należy zainstalować osobno, niemniej również tutaj próg wejścia jest niski. Wynika to z faktu, że dostępne są kontenery Docker, takie jak IIC-OSIC-TOOLS, które zawierają kompletne środowisko: narzędzia EDA, PDK oraz przykładowe projekty.

– Interesujący jest także sam proces rozwoju naszego open-source PDK. Dzięki publicznej dostępności technologii IHP wzbudził on zainteresowanie wielu nowych użytkowników oraz instytucji. Otrzymaliśmy również liczne informacje zwrotne od ekspertów, co pozwoliło – i nadal pozwala – na ciągłe podnoszenie jakości naszych bibliotek – zaznacza dr Krzysztof Herman.

– Dla IHP podejście open source okazało się strzałem w dziesiątkę również pod względem marketingowym. Gdyby w Polsce Cezamat PW lub inne laboratoria związane z arsenkiem galu zdecydowały się na podobny krok, z pewnością zwiększyłyby swoją rozpoznawalność. Dziś ma to kluczowe znaczenie.

To oznacza, że wyniki pomiarów można konsultować na forum?

– W starszym modelu, jeśli jakaś firma rozwijała tego typu bloczki, inżynierowie nie mogli rozmawiać o nich poza pokojem, w którym zajmowali się ich tworzeniem. Żaden z nich nie potrafił połączyć tych elementów w całość. W IHP natomiast, nawet 100% projektu jest udostępniana przez open source. Testowaniem zajmuje się środowisko. Wskazują ewentualne błędy i sugerują, co trzeba poprawić. Pracują z nami ludzie z całego świata, przy okazji projektowania układów scalonych na swoje potrzeby. Ich wiedza i umiejętności są dla nas bardzo wartościowe, bo weryfikują nasze rozwiązania w swoich projektach i przeprowadzają symulacje, bazując na swoim doświadczeniu.

Projektują również ułożenie masek do wytrawiania?

– Zgadza się. Na bardzo niskim poziomie, na przykład podczas projektowania układów analogowych, praca na krzemie sprowadza się głównie do wymiarowania przyrządów półprzewodnikowych. Ich szerokość i długość determinują określone parametry elektryczne, które są kluczowe z punktu widzenia działania układu. Każdy przyrząd składa się z wielu warstw – a tych warstw jest naprawdę dużo. Samych przyrządów mogą być setki, dziesiątki tysięcy, a nawet więcej – łatwo się w tym pogubić. Na szczęście edytory do projektowania masek, takie jak KLayout, umożliwiają podejście modułowe. Wystarczy pobrać odpowiedni element z panelu, nadać mu właściwe parametry geometryczne i umieścić w odpowiednim miejscu projektu – podobnie jak mebel we wspomnianej aplikacji do projektowania wnętrz.

– Jako ciekawostkę mogę dodać, że w IHP działa oddzielny zespół zajmujący się przetwarzaniem plików GDS (zawierających geometryczne reprezentacje warstw, struktur i połączeń w układach półprzewodnikowych) na maski, będące odpowiednikiem negatywów w fotografii. To właśnie te maski wysyłamy wraz z zamówieniem do podwykonawcy.

Czy Open Source Silicon może zainteresować polskich inżynierów?

– Nie jestem pewien – liczę tu raczej na ludzką ciekawość. Przeszliśmy pewną przemianę kulturową, a model nauczania wydaje się być już częściowo wyczerpany i funkcjonuje siłą bezwładności. Być może inżynierowie dostrzegą w tym nowym podejściu konkretne korzyści dla siebie. Najważniejsze jest to, aby rozumieli, dlaczego to robią, i przestali postrzegać projektowanie układów scalonych jako coś skrajnie skomplikowanego. W tym kontekście trudno nie wspomnieć o roli sztucznej inteligencji, która – odpowiednio „nakarmiona” informacjami o naszym PDK – może skutecznie pomagać w zrozumieniu modeli oraz wspierać proces projektowania.

– Istnieje również problem zaufania – często pojawia się przekonanie, że jeśli coś jest darmowe, to zapewne jest niskiej jakości. Tymczasem z naszej linii produkcyjnej zeszły działające układy scalone, takie jak: Basilisk (64-bitowy, zdolny do uruchomienia systemu Linux SoC), Greyhound (RISC-V SoC z FPGA o 1024 LUT) czy TTIHP25a – projekt integrujący ponad 500 małych, multipleksowanych projektów edukacyjnych. Wszystkie te układy zostały zaprojektowane wyłącznie z użyciem rozwiązań open source – podkreśla dr Krzysztof Herman.

Być może w taki sposób więcej inżynierów zdobędzie kompetencje do projektowania układów scalonych?

– Tak, do tego się to sprowadza. Narzędzia, PDK oraz podstawowe bloki IP są już dostępne, a będzie tylko lepiej dzięki projektom, które właśnie zostały zapoczątkowane. Już dziś można na własnym laptopie projektować funkcjonalne układy scalone i tworzyć kolejne iteracje w krzemie. Jeśli w całym cyklu pojawi się błąd, z dużym prawdopodobieństwem zostanie on wykryty i usunięty.

– W ten sposób inżynierowie mogą nie tylko stosunkowo niskim kosztem nauczyć się projektowania chipów, lecz także rozwijać prototypy produktów, zwiększając tym samym konkurencyjność swoich firm na rynku. Kompetencje w dziedzinie projektowania to tylko wycinek rzeczywistości a open-source pozwala rozwinąć skrzydła na innych poziomach takich jak rozwój narzędzi EDA, rozwój modeli automatyzacja procesu projektowania etc.

– Sama inicjatywa open-source silicon wywodzi się z problemu prognozowanego niedoboru kadr w Stanach Zjednoczonych, co skłoniło Google do sfinansowania otwartych inicjatyw PDK oraz MPW we współpracy ze SkyWater i GlobalFoundries. Problem ten wciąż nie został w pełni rozwiązany, jednak widać już pewne oznaki poprawy.

– Być może w przyszłości warszawski Cezamat PW w większym stopniu wykorzysta swoje możliwości infrastrukturalne, a źródłem kadr staną się inżynierowie wychowani na rozwiązaniach open source, którzy rozwijali swoje kompetencje dzięki otwartemu dostępowi do wiedzy.

Open source silicon to nie tylko narzędzia i biblioteki. To zmiana sposobu myślenia o projektowaniu układów scalonych – z zamkniętego i elitarnego na otwarty i dostępny dla każdego – podsumowuje dr Krzysztof Herman.

Chipathon SSCS PICO 2026 – konkurs na projekt układu scalonego typu open source

Chipathon SSCS PICO 2026 – konkurs na projekt układu scalonego typu open source  DigiKey uruchamia serię filmów „Engineering Unlocked” o przyszłości projektowania układów elektronicznych

DigiKey uruchamia serię filmów „Engineering Unlocked” o przyszłości projektowania układów elektronicznych  NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W

NanoIC otwiera dostęp do pierwszych w historii hybrydowych połączeń między-układowych; zestaw do projektowania (PDK) połączeń typu RDL i D2W