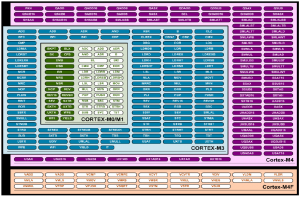

Migracja z Cortex-M3 do Cortex-M4

Tabela ta pokazuje, że w większości funkcjonalności Cortex-M3 i Cortex-M4 są takie same, z tą różnicą, że Cortex-M4 posiada dodatkowo rozszerzenia DSP oraz opcjonalną jednostkę FPU. Do migracji z M3 do M4 prawie nie ma potrzeby modyfikowania sprzętu i oprogramowania. W następnych rozdziałach zostanie szczegółowo omówiony rdzeń Cortex-M4, z naciskiem na jego możliwości cyfrowego przetwarzania sygnałów.

Model dla programistów

Tryby pracy

Cortex-M4, tak samo jak Cortex-M3, obsługuje dwa tryby pracy: tryb wątkowy (normalny) (Thread Mode) oraz tryb obsługi przerwania (Handler Mode). Rdzeń przechodzi w tryb wątkowy po resecie lub w wyniku zwrócenia wyjątku. W trybie wątkowym kod może być wykonywany na dwóch poziomach o różnych prawach dostępu: uprzywilejowanym i nieuprzywilejowanym. Rdzeń przechodzi do trybu obsługi przerwania w wyniku wystąpienia wyjątku. W trybie obsługi przerwania cały kod jest na poziomie uprzywilejowanym.

Stany pracy

Cortex-M4, tak samo jak Cortex-M3, może pracować w jednym z dwóch stanów pracy: Thumb oraz Debug. Stan pracy Thumb jest normalnym wykonywaniem instrukcji Thumb na 16- i 32-bitowych wyrównanych półsłowach. Stan Debug jest stanem, gdy rdzeń jest w trakcie debugowania.

Zestaw instrukcji

Cortex-M4, wykorzystuje tę samą architekturę, jak Cortex-M3, czyli architekturę ARMv7-M. Instrukcje tych rdzeni pochodzą z zestawu instrukcji Thumb-2, który zawiera instrukcje 16- i 32-bitowe. Dodatkowo, Cortex-M4 posiada instrukcje SIMD oraz opcjonalne instrukcje operacji na liczbach zmiennoprzecinkowych, które zwiększają łączną liczbę instrukcji, do 291 (w porównaniu do 186 instrukcji rdzenia Cortex-M3) (rysunek 2).

Rys. 2.

Na rysunku powyżej pokazano zależności między instrukcjami rodziny Cortex-M. ISA (Instruction Set Architecture) Cortex-M3 jest kompatybilny z ISA Cortex-M4, a Cortex-M4F (rdzeń Cortex-M4 z jednostką FPU) powstał przez dodanie instrukcji FPU do podstawowej wersji Cortex-M4.

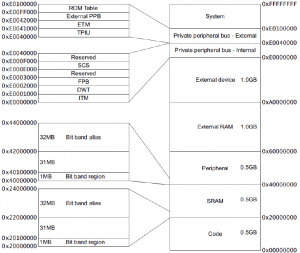

Przestrzeń adresowa

Cortex-M3 i Cortex-M4 mają tę samą przestrzeń adresową (rysunek 3).

Rys. 3.

ROM Table – Tabela ROM

External PPB – PPB zewnętrzny

Reserved – Zarezerwowane

Bit band alias – Alias pasma bitowego

Bit band region – Region pasma bitowego

Private peripherial bus – External – Prywatna magistrala peryferyjna – zewnętrzna

Private peripherial bus – Internal – Prywatna magistrala peryferyjna – wewnętrzna

External device – Urządzenia zewnętrzne

External RAM – Zewnętrzna RAM

Peripheral – Peryferia

Code – Kod

Uzyskiwanie dostępu w paśmie bitowym (Bit Banding)

Cortex-M4, tak samo jak Cortex-M3, zapewnia dostęp bitowy do dwóch regionów pamięci, jednego w wewnętrznym obszarze SRAM i drugiego w obszarze peryferyjnym. Każde słowo w tych regionach jest przyporządkowane (aliasowane) do konkretnego bitu w odpowiadającym regionie pasma bitowego. Czytanie z regionu aliasowego zwraca słowo zawierające wartość odpowiadającego bitu. Zapisywanie słowa w regionie aliasowym daje w wyniku atomowy odczyt/modyfikację/zapis odpowiadającego bitu w regionie pasma bitowego.

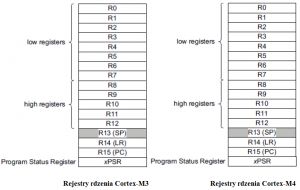

Porównanie rejestrów rdzeni

Cortex-M4, tak samo jak Cortex-M3, ma 16 rejestrów ogólnego przeznaczenia, od R0 do R15 – wszystkie 32-bitowe. Rejestry od R0 do R12 są ogólnie dostępne dla wszystkich instrukcji. R13 jest używany jako wskaźnik stosu, R14 jako rejestr połączenia (do podprogramu i zwrócenia wyjątku), a R15 jako licznik programu. Na rysunku 4 przedstawiono porównanie rejestrów rdzeni Cortex-M3 i Cortex-M4:

Rys. 4.

low registers – Rejestry młodsze

high registers – Rejestry starsze

Program Status Register – Rejestr statusu programu

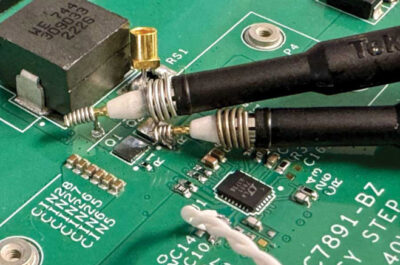

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary

Projekty inteligentnych sterowników przetwornic buck z tranzystorami GaN — część 1: Zagadnienia i pomiary  Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze

Prof. Ryszard Tadeusiewicz: Sztuczna inteligencja wykorzystująca seks w komputerze  Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)

Grzegorz Kamiński: Historia pewnej płytki krzemowej 300 mm (12”)